## SRM VALLIAMMAI ENGINEERING / COLLEGE

(An Autonomous Institution)

SRM Nagar, Kattankulathur-603203

### DEPARTMENT OF INFORMATION TECHNOLOGY

ACADEMIC YEAR: 2020-2021

ODD SEMESTER

### **LAB MANUAL**

(REGULATION - 2019)

# 1908306-DIGITAL SYSTEMS AND COMMUNICATION LABORATORY

THIRD SEMESTER

B.Tech - Information Technology

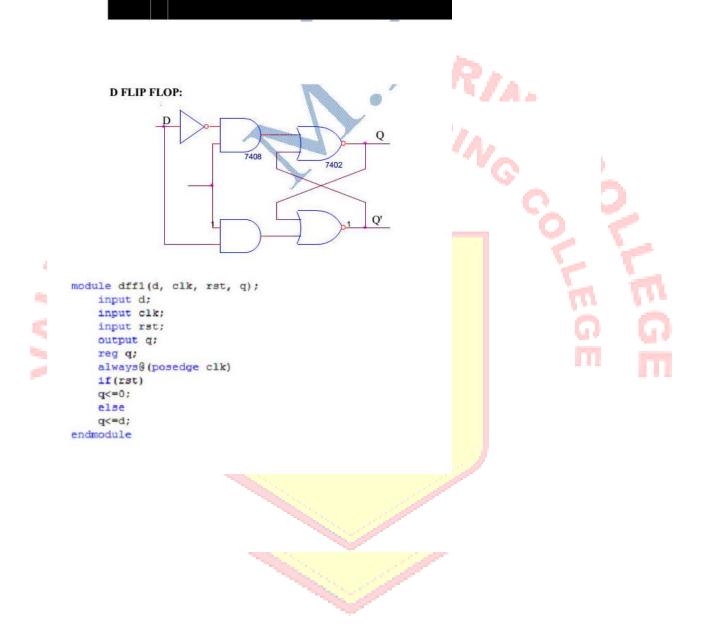

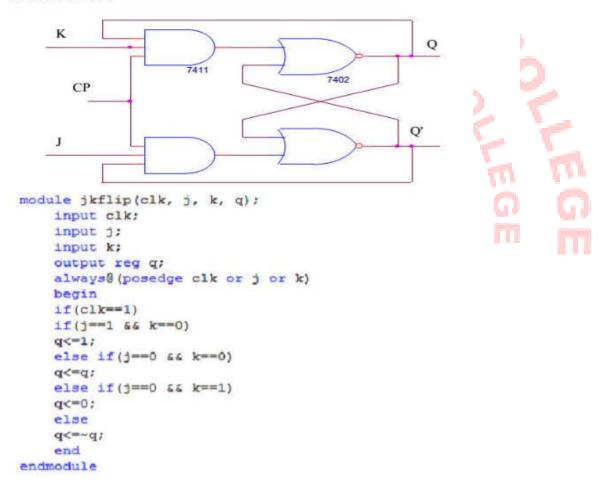

Prepared by

Ms.S.Shenbagavadivu Mr.R.Sankaranarayanan

| E.NO | EXPERIMENT NAME                                                                            | Pg. No. |  |  |

|------|--------------------------------------------------------------------------------------------|---------|--|--|

| A    | PE0,PO,PSO                                                                                 | 03-05   |  |  |

| В    | Syllabus with co-po matrix                                                                 |         |  |  |

| С    | Co, Co-Po Matrix, Co-PSO Matrix                                                            | 07      |  |  |

| D    | Mode of Assessment                                                                         | 08      |  |  |

| E    | Introduction/ Description of major software & Hardware involved in lab                     | 09-12   |  |  |

| F    | Study And Verification Of Boolean Logic Gates                                              | 11 – 14 |  |  |

| 1    | Verification of Boolean Theorems using basic gates                                         | 15 – 21 |  |  |

| 2    | Design and implement Half/Full Adder and Subtractor.                                       | 22 – 29 |  |  |

| 3    | Design and implement combinational circuits using MSI devices- checker  Parity generator / | 30 – 34 |  |  |

| 4    | Design and implement shift-registers.                                                      | 35 – 39 |  |  |

| 5    | Design and implement synchronous counters.                                                 | 40 – 47 |  |  |

| 6    | Amplitude modulation and demodulation                                                      | 48 – 52 |  |  |

| 7    | Frequency modulation and demodulation                                                      | 53 – 57 |  |  |

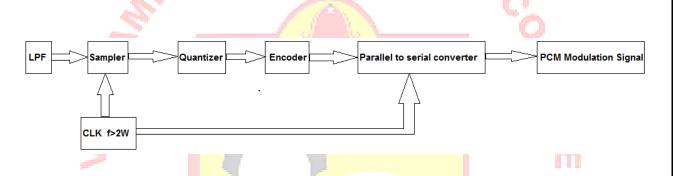

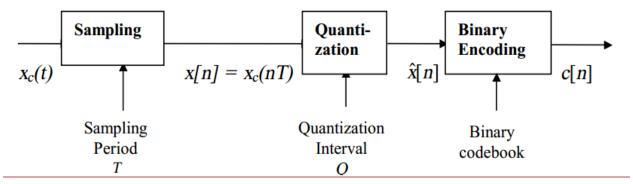

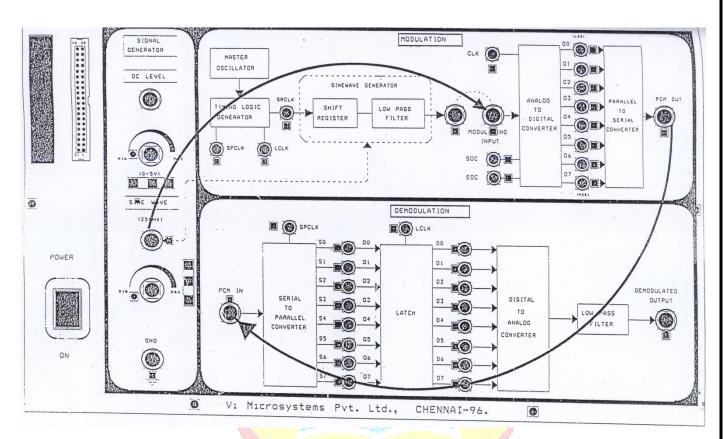

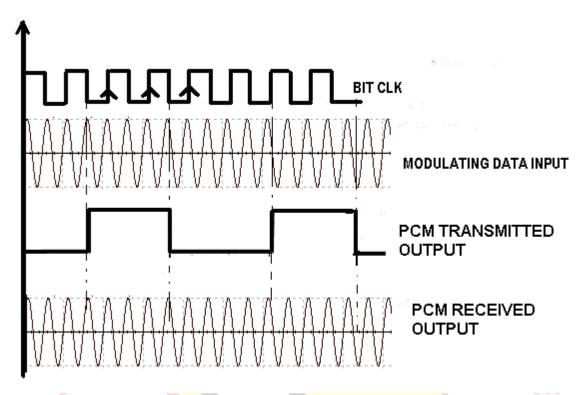

| 8    | Pulse code modulation and demodulation.                                                    | 58 – 62 |  |  |

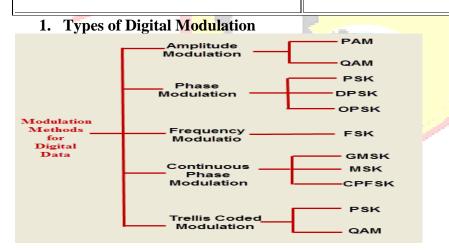

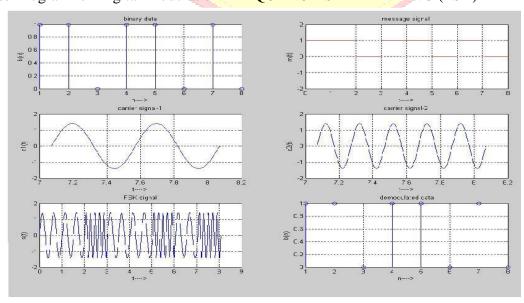

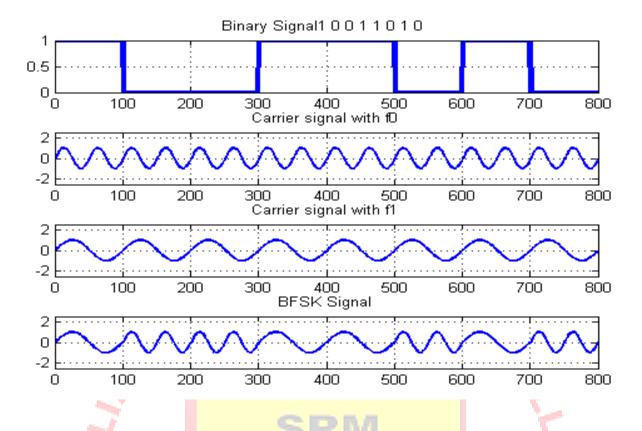

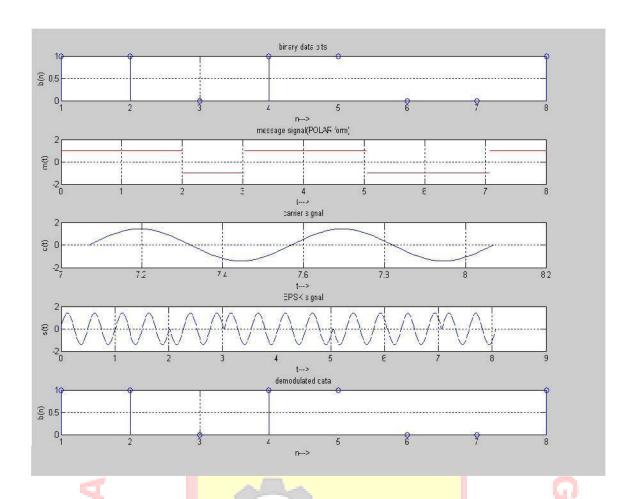

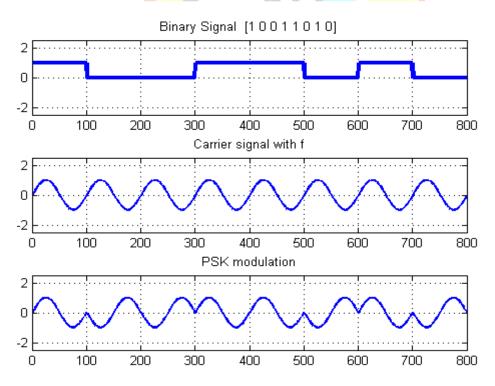

| 9    | FSK, PSK and DPSK schemes (Simulation                                                      |         |  |  |

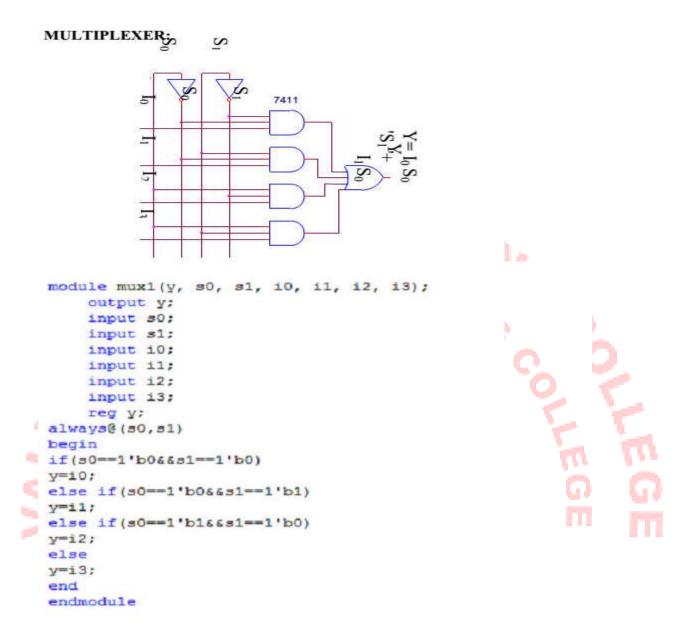

| 10   | Coding combinational circuits using HDL                                                    |         |  |  |

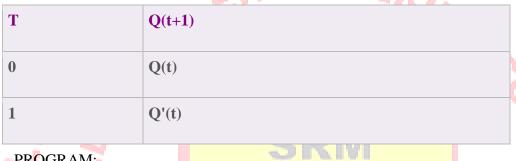

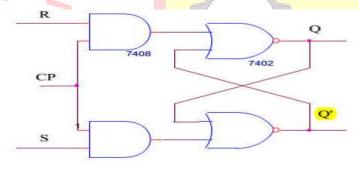

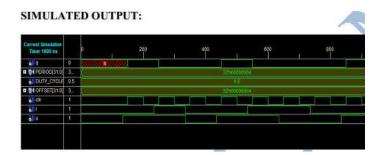

| 11   | Coding sequential circuits using HDL.                                                      | 79 – 84 |  |  |

| 12   | TBS – Introduction to Internet of Things                                                   | 85 – 86 |  |  |

### PROGRAMME EDUCATIONAL OBJECTIVES (PEOs)

- 1. To afford the necessary background in the field of Information Technology to deal with engineering problems to excel as engineering professionals in industries.

- 2. To improve the qualities like creativity, leadership, teamwork and skill thus contributing towards the growth and development of society.

- 3. To develop ability among students towards innovation and entrepreneurship that caters to the needs of Industry and society.

- 4. To inculcate and attitude for life-long learning process through the use of information technology sources.

- 5. To prepare then to be innovative and ethical leaders, both in their chosen profession and in other activities.

### **PROGRAMME OUTCOMES (POs)**

After going through the four years of study, Information Technology Graduates will exhibit ability to:

| DO# | C 1 4 44 7 4                      | D 0.4                                                                                     |

|-----|-----------------------------------|-------------------------------------------------------------------------------------------|

| PO# | Graduate A <mark>ttrib</mark> ute | Programme Outcome                                                                         |

| 1   | Engineering knowledge             | Apply the knowledge of mathematics, science, engineering fundamentals, and an engineering |

|     |                                   | specialization for the solution of complex engineering                                    |

|     |                                   | problems.                                                                                 |

| 2   | Problem analysis                  | Identify, formulate, research literature, and analyze                                     |

|     |                                   | complex engineering problems reaching substantiated                                       |

|     |                                   | conclusions using first principles of mathematics, natural                                |

|     |                                   | sciences, and engineering sciences.                                                       |

| 3   | Design/development of             | Design solutions for complex engineering problems and                                     |

|     | solutions                         | design system components or processes that meet the                                       |

|     |                                   | specified needs with appropriate consideration for public                                 |

|     |                                   | health and safety, and cultural, societal, and                                            |

|     |                                   | environmental considerations.                                                             |

| 4   | Conduct investigations of         | Use research-based knowledge and research methods                                         |

|     | complex problems                  | including design of experiments, analysis and                                             |

|     |                                   | interpretation of data, and synthesis of the information to                               |

|    |                                | provide valid conclusions                                                                                                                                                                                                                                                             |

|----|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5  | Modern tool usage              | Create, select, and apply appropriate techniques, resources, and modern engineering and IT tools, including prediction and modeling to complex engineering activities, with an understanding of the limitations.                                                                      |

| 6  | The engineer and society       | Apply reasoning informed by the contextual knowledge to assess societal, health, safety, legal, and cultural issues and the consequent responsibilities relevant to the professional engineering practice                                                                             |

| 7  | Environment and sustainability | Understand the impact of the professional engineering solutions in societal and environmental contexts, and demonstrate the knowledge of, and need for sustainable development.                                                                                                       |

| 8  | Ethics                         | Apply ethical principles and commit to professional ethics and responsibilities and norms of the engineering practice                                                                                                                                                                 |

| 9  | Individual and team work       | Function effectively as an individual, and as a member or leader in diverse teams, and in multidisciplinary settings                                                                                                                                                                  |

| 10 | Communication                  | Communicate effectively on complex engineering activities with the engineering community and with the society at large, such as, being able to comprehend and write effective reports and design documentation, make effective presentations, and give and receive clear instructions |

| 11 | Project management and finance | Demonstrate knowledge and understanding of the engineering and management principles and apply these to one's own work, as a member and leader in a team, to manage projects and in multidisciplinary environments                                                                    |

| 12 | Life-long learning             | Recognize the need for, and have the preparation and ability to engage in independent and life-long learning in the broadest context of technological change                                                                                                                          |

### PROGRAM SPECIFIC OUTCOMES (PSOs)

By the completion of Information Technology program the student will have following Program specific outcomes

- 1. Design secured database applications involving planning, development and maintenance using state of the art methodologies based on ethical values.

- 2. Design and develop solutions for modern business environments coherent with the advanced technologies and tools.

- 3. Design, plan and setting up the network that is helpful for contemporary business environments using latest hardware components.

- **4.** Planning and defining test activities by preparing test cases that can predict and correct errors ensuring a socially transformed product catering all technological needs.

### 908306 DIGITAL SYSTEMS AND COMMUNICATION LABORATORY

LTPC 0021

### **OBJECTIVES:**

- Understanding the concept of basic gates.

- Develop a circuit for combinational and sequential circuits.

- Get a deep understanding on analog modulation technques.

- Learn the concept of digital modulation techniques.

- Understand the working principle of HDL.

- Design and develop basic adigital and communication circuits.

### LIST OF EXPERIMENTS

- 1. Verification of Boolean Theorems using basic gates.

- 2. Design and implement Half/Full Adder and Subtractor.

- 3. Design and implement combinational circuits using MSI devices- Parity generator / checker

- 4. Design and implement shift-registers.

- 5. Design and implement synchronous counters.

- 6. Amplitude modulation and demodulation

- 7. Frequency modulation and demodulation

- 8. Pulse code modulation and demodulation.

- 9. FSK, PSK and DPSK schemes (Simulation)

- 10. Coding combinational circuits using HDL.

- 11. Coding sequential circuits using HDL.

**TOTAL: 45 PERIODS**

### **COURSE OUTCOMES**

| 1908306.1 | Design a basic combinational circuit applications.        |

|-----------|-----------------------------------------------------------|

| 1908306.2 | Design a basic analog modulation circuits AM,FM.          |

| 1908306.3 | Simukate a FSK,PSK circuits in HDL.                       |

| 1908306.4 | Construct a pulse code modulation circuits.               |

| 1908306.5 | Code and Simulate a combinational and sequential circuits |

### **CO-PO MATRIX**

| CO-PO MATRIX            |     | , E | N   | GII | NE  | E      | ?/A |     |     |      |      |      |

|-------------------------|-----|-----|-----|-----|-----|--------|-----|-----|-----|------|------|------|

| CO                      | PO1 | PO2 | PO3 | PO4 | PO5 | PO6    | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 |

| 1908306.1               | 3   | 2   | 3   | -   | 2   |        | -   | -   | - ( | 3.   | -    | -    |

| 1908306.2               | 2   | 3   | 3   |     | 2   | ΞØ,    | _   | -   | -   | 7    | -    | -    |

| 1908306.3               | 3   | 3   | 3   | - ( | 2   | RIV    | -   | -   | -   | -    | r.   | -    |

| 1908306.4               | 3   | 3   | 3   | Z.  | 2   | -      | -   | -   | -   | - (  | 5    | -    |

| 1908306 <mark>.5</mark> | 2   | 2   | 2   | _   | 2   | Jan. 1 |     | _   | -   | -    | 11 - | -    |

| 1908306                 | 3   | 3   | 3   |     | 2   | البا   | -   | -   | -   | -    | -    | -    |

### CO-PSO MATRIX

| COURSE    | PSO 1 |

|-----------|-------|

| 1908306.1 | 3     |

| 1908306.2 | 3     |

| 1908306.3 | 3     |

| 1908306.4 | 2     |

| 1908306.5 | 3     |

| 1908306   | 3     |

### MODE OF ASSEMENT EVALUATION PROCEDURE FOR EACH EXPERIMENTS

| S.No | Description              | Mark |

|------|--------------------------|------|

| 1.   | Aim & Pre-Lab discussion | 20   |

| 2.   | Observation              | 20   |

| 3.   | Conduction and Execution | 30   |

| 4.   | Output & Result          | 10   |

| 5.   | Viva                     | 20   |

| 4    | Total                    | 100  |

SRM

### INTERNAL ASSES<mark>SMENT FOR LABORATORY</mark>

| S.No | Description                          | Mark |

|------|--------------------------------------|------|

| 1.   | Conduction & Execution of Experiment | 25   |

| 2.   | Record                               | 10   |

| 3.   | Model Test                           | 15   |

|      | Total                                | 50   |

### INTRODUCTION/ DESCRIPTION OF MAJOR SOFTWARE & HARDWARE INVOLVED IN LAB

### LIST OF EQUIPMENT FOR A BATCH OF 30 STUDENTS

### **HARDWARE**

- ✓ Digital trainer kits -30 Nos.

- ✓ Kits for AM, FM and PCM

- ✓ Signal generator / Function generators / Power Supply / CRO / Bread Board each -15 Nos.

- ✓ Digital ICs required for the experiments in sufficient numbers.

### **SOFTWARE**

- ✓ HDL simulator.

- ✓ MATLAB / SCILAB for simulation experiments PCs 10 Nos.

### **OUTCOME**

- ✓ Design a basic combinational circuit applications.

- ✓ Design a basic analog modulation circuits AM,FM.

- ✓ Simulate a FSK,PSK circuits in HDL.

- ✓ Construct a pulse code modulation circuits.

- ✓ Code and Simulate a combinational circuits and sequental circuits.

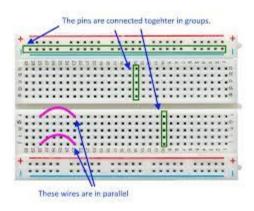

### **BREADBOARD**

An electronics breadboard is actually referring to a solder less breadboard. These are great units for making temporary circuits and prototyping, and they require absolutely no soldering. Prototyping is the process of testing out an idea by creating a preliminary model from which other forms are developed or copied, and it is one of the most common uses for breadboards

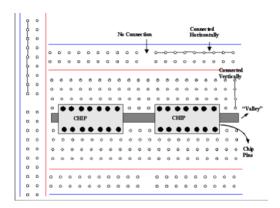

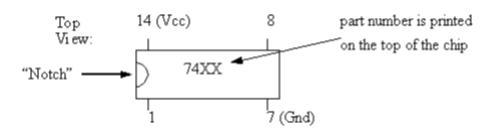

### Transistor-Transistor Logic (TTL)

TTL refers to the nature of the circuit of the digital logic gate; All of the TTL chips you will use are "Dual In-line Packages" or DIPs. Most of the packages are 14 pins, and the pins are number from looking at the chip from the top: Below the "notch" is pin 1 to pin 7, and above the notch is pin 14 down to 8. NOTE that Pin 14 must always be connected to VCC (+5V) and pin 7 to ground (0V)

NEER/NG

### PRINTED CIRCUIT BOARD

PCBs can be single-sided (one copper layer), double-sided (two copper layers on both sides of one substrate layer), or multi-layer (outer and inner layers of copper, alternating with layers of substrate). A basic PCB consists of a flat sheet of insulating material and a layer of copper foil,

laminated to the substrate. Chemical etching divides the copper into separate conducting lines called tracks or *circuit traces*, pads for connections, vias to pass connections between layers of copper, and features such as solid conductive areas for EM shielding or other purposes. The tracks function as wires fixed in place, and are insulated from each other by air and the board substrate material. The surface of a PCB may have a coating that protects the copper from corrosion and reduces the chances of solder shorts between traces or undesired electrical contact with stray bare wires. For its function in helping to prevent solder shorts, the coating is called solder resist.

### MODELSIM HDL SIMULATOR:

The original Modeltech (VHDL) simulator was the first mixed-language simulator capable of simulating VHDL and Verilog design entities together. In 2003, ModelSim 5.8 was the first simulator to begin supporting features of the Accellera SystemVerilog 3.0 standard.[1] In 2005 Mentor introduced Questa to provide high performance Verilog and SystemVerilog simulation and expand Verification capabilities to more advanced methodologies such as Assertion Based Verification and Functional Coverage. Today Questa is the leading high performance SystemVerilog and Mixed simulator supporting a full suite of methodologies including industry standard OVM and UVM. ModelSim is still the leading simulator for FPGA design.

### LANGUAGE SUPPORT FOR MODELSIM:

- VHDL

- Verilog

- Verilog 2001

- SystemVerilog

- PSL

- SystemC

### STUDY AND VERIFICATION OF BOOLEAN LOGIC GATES

### AIM:

To draw a pin diagram and truth table for the basic logic gates and also verify its truth table

#### THEORY:

Circuit that takes the logical decision and the process are called logic gates. Each gate has one or more input and only one output. In digital system processing the Boolean function by using basic gates (such as OR, AND, NOT gates). All Basic gates form these universal gates. NAND, NOR and X-OR are known as universal gates.

- ❖ OR GATE: The OR gate performs a logical addition commonly known as OR function. The output is high when any one of the inputs is high. The output is low level when both the inputs are low.

- \* AND GATE: The AND gate performs a logical multiplication commonly known as AND function. The output is high when both the inputs are high. The output is low level when any one of the inputs is low.

- \* NOT GATE: The NOT gate is called an inverter. The output is high when the input is low. The output is low when the input is high.

- \* NAND GATE: The NAND gate is a contraction of AND-NOT. The output is high when both inputs are low and any one of the input is low. The output is low level when both inputs are high.

- \* NOR GATE: The NOR gate is a contraction of OR-NOT. The output is high when both inputs are low. The output is low when one or both inputs are high.

- **X-OR GATE:** The output is high when any one of the inputs is high. The output is low when both the inputs are low and both the inputs are high.

### **APPARATUS REQUIRED:**

| SL  | COMPONENT       | SPECIFICATION | QTY |

|-----|-----------------|---------------|-----|

| No. | <del>-</del>    |               |     |

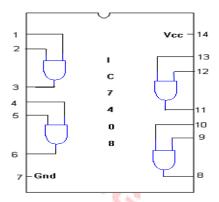

| 1.  | AND GATE        | IC 7408       | 1   |

| 2.  | OR GATE         | IC 7432       | 1   |

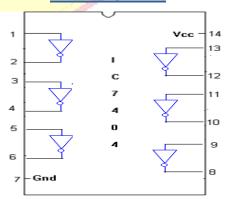

| 3.  | NOT GATE        | IC 7404       | 1   |

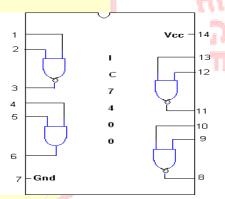

| 4.  | NAND GATE 2 I/P | IC 7400       | 1   |

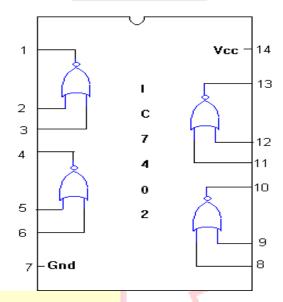

| 5.  | NOR GATE        | IC 7402       | 1   |

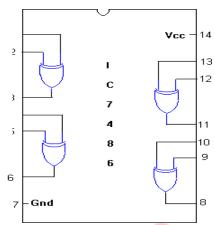

| 6.  | X-OR GATE       | IC 7486       | 1   |

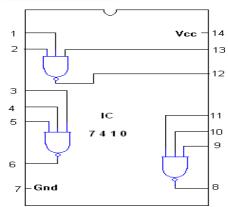

| 7.  | NAND GATE 3 I/P | IC 7410       | 1   |

| 8.  | IC TRAINER KIT  | -             | 1   |

| 9.  | PATCH CORD      | -             | 14  |

### **CIRCUIT & TRUTH TABLE:**

### **AND GATE**

### **SYMBOL:**

### Y=A.B

TRUTH TABLE

| А | В | А.В |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | o   |

| 1 | 1 | 1   |

### **PIN DIAGRAM:**

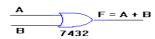

#### SYMBOL:

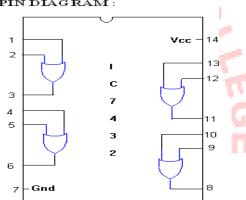

### **OR GATE**

#### TRUTH TABLE

| Α | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

### **NOT GATE**

### **SYMBOL**:

### **PIN DIAGRAM:**

### TRUTH TABLE:

| Α | A |

|---|---|

| 0 | 1 |

| 1 | n |

### **XOR GATE**

### **SYMBOL**:

TRUTH TABLE:

| А | В | AB + AB |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

### **PIN DIAGRAM:**

### **2INPUT NAND GATE**

### **SYMBOL**:

### PIN DIAGRAM:

### SRM

TRUTH TABLE

| А | В | A.B |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

### **3INPUT NAND GATE**

SYMBOL:

TRUTH TABLE

| Α | В | С | A.B.C |

|---|---|---|-------|

| 0 | D | 0 | 1     |

| 0 | D | 1 | 1     |

| o | 1 | 0 | 1     |

| 0 | 1 | 1 | 1     |

| 1 | D | 0 | 1     |

| 1 | 0 | 1 | 1     |

| 1 | 1 | 0 | 1     |

| 1 | 1 | 1 | 0     |

#### PIN DIAGRAM:

### **NOR GATE**

### SYMBOL:

### TRUTH TABLE

| Α | В | A+B |

|---|---|-----|

| 0 | 0 | 1   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

### PIN DIAGRAM:

### SRM

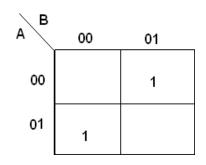

### **PROCEDURE:**

- (i) Connections are given as per pin diagram along with GND & VCC

- (ii) Logical inputs are given as per circuit diagram.

- (iii) Observe the output and verify the truth table for each gate

### **RESULT:**

Thus the logic gates and it's the truth table is verified successfully.

### **EX.NO 1:** Verification of Boolean Theorems using basic gates

### **AIM**

To verify the Boolean theorem using logic gates and it's the truth table

### **THEORY**

A set of rules or Laws of Boolean Algebra expressions have been invented to help reduce the number of logic gates needed to perform a particular logic operation resulting in a list of functions or theorems known commonly as the Laws of Boolean Algebra. Boolean Algebra is the mathematics we use to analyse digital gates and circuits.

### **BOOLEAN LAWS**

- The basic Laws of Boolean Algebra that relate to the Commutative Law allowing a change in position for addition and multiplication, the Associative Law allowing the removal of brackets for addition and multiplication, as well as the Distributive Law allowing the factoring of an expression, are the same as in ordinary algebra.

- The variables used in Boolean Algebra only have one of two possible values, a logic "0" and a logic "1" but an expression can have an infinite number of variables all labelled individually to represent inputs to the expression

- Boolean algebra is a mathematical system consisting of a set of two or more distinct elements, two binary operators denoted by the symbols (+) and (.) and one unary operator denoted by the symbol either bar (-) or prime ('). They satisfy the commutative, associative, distributive and absorption properties of the Boolean algebra.

### **Commutative Property**

- ✓ Boolean addition is commutative, given by A+B=B+A

- ✓ Boolean algebra is also commutative over multiplication, given by A.B=B.A

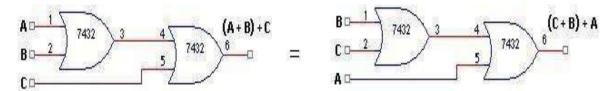

- ✓ The associative property of addition is given by A+(B+C)=(A+B)+C

- $\checkmark$  The associative law of multiplication is given by A. (B.C) = (A.B).C

### **Distributive Property**

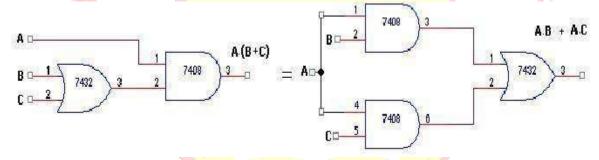

✓ The Boolean addition is distributive over Boolean multiplication,

given by

$$A+BC = (A+B)(A+C)$$

✓ Boolean multiplication is also distributive over Boolean addition given by A. (B+C) = A.B+A.C

### De Morgan's Therem

✓ First Theorem

It states that the complement of a product is equal to the sum of the complements.

$$(AB)' = A' + B'$$

✓ Second Theorem

It states that the complement of a sum is equal to the product of the complements. (A+B)' = A'.B'

### **Idempotent Law**

$$X + X = X X \bullet X = X$$

### **Involution Law**

$$(X')' = X$$

### **Absorption Law**

$$X + XY = X X(X + Y) = X$$

### **Consensus theorem**

$$XY + X'Z + YZ = XY + X'Z$$

### **APPARATUS REQUIRED:**

| S.N<br>O | COMPONENTS             | RANGE | QUANTIT<br>Y |

|----------|------------------------|-------|--------------|

| 1        | Digital IC trainer kit | -     | 1            |

|          |                        | 7400  | 1            |

|          |                        | 7402  | 1            |

|          |                        | 7404  | 1            |

| 2        | IC                     | 7408  | 1            |

| 2        |                        | 7432  | 1            |

|          | -N                     | 7486  | Ed.          |

| 3        | Bread board            | -     | -"4/N        |

| 4        | Connecting wires       | -     | As required  |

### CIRCUIT DIAGRAM & TRUTH TABLE:

### a) Commutative Law

Truth Table

| In | put | Output  |   |  |  |

|----|-----|---------|---|--|--|

| A  | В   | A+B B+A |   |  |  |

| 0  | 0   | 0       | 0 |  |  |

| 0  | 1   | 1       | 1 |  |  |

| 1  | 0   | 1       | 1 |  |  |

| 1  | 1   | 1       | 1 |  |  |

### b) Associative Law

**Truth Table**

|     | Input | t | Output |         |      |         |

|-----|-------|---|--------|---------|------|---------|

| A   | В     | C | A+B    | (A+B)+C | B+C  | A+(B+C) |

| 0   | 0     | 0 | 0      | 0       | 0    | 0       |

| 0   | 0     |   | 0      | 1       | 714, | 1       |

| 0   | 1     | 0 | 1      | 1       | 1    | 1       |

| 0   | 1     | 1 | 1      | 1       | 1    | 1       |

| 1 . | 0     | 0 | 1      | 1       | 0    | 1       |

| 14  | 0     | 1 | 1      | 1       | 1    | 1       |

| 4-  | 1     | 0 | 1-/    | 1       | 1    | 1       |

| _1% | 1     | 1 | 1      | 1       | 1    | 1       |

### c) <u>Distributive Law</u>

**Truth Table**

|   |       | 75 |        |                 |     |     |        |

|---|-------|----|--------|-----------------|-----|-----|--------|

|   | Input |    | Output |                 |     |     |        |

| A | В     | C  | B+C    | <b>A.</b> (B+C) | A.B | A.C | A.B+A. |

| 0 | 0     | 0  | 0      | 0               | 0   | 0   | 0      |

| 0 | 0     | 1  | 1      | 0               | 0   | 0   | 0      |

| 0 | 1     | 0  | 1      | 0               | 0   | 0   | 0      |

| 0 | 1     | 1  | 1      | 0               | 0   | 0   | 0      |

| 1 | 0     | 0  | 0      | 0               | 0   | 0   | 0      |

| 1 | 0     | 1  | 1      | 1               | 0   | 1   | 1      |

| 1 | 1     | 0  | 1      | 1               | 1   | 0   | 1      |

| 1 | 1     | 1  | 1      | 1               | 1   | 1   | 1      |

### **d**)De-Morgan's Theorem 1:

### CNGINEED.

### Truth Table:

### 1. Observation table for First Theorem of Demorgan

| Inp | nput Out |        | put   |  |

|-----|----------|--------|-------|--|

| A B |          | (A+B)' | A'. B |  |

| 0   | 0        | 1      | 1     |  |

| 0   | 1        | 0      | 0     |  |

| 1   | 0        | 0      | 0     |  |

| 1   | 1        | 0      | 0     |  |

| In | put | ut Output   |             |

|----|-----|-------------|-------------|

| Α  | В   | LHS = A + B | RHS = A . B |

| 0  | 0   |             | 8           |

| 0  | 1   |             |             |

| 1  | 0   |             |             |

| 1  | 1   |             |             |

### e) De-Morgan's Theorem: 2

### **Truth Table**

### 2. Observation table for Second Theorm of Demorgan

| Inj | put | Out        | put |

|-----|-----|------------|-----|

| A   | В   | (A.B)' A'+ |     |

| 0   | 0   | 1          | 1   |

| 0   | 1   | 1          | 1   |

| 1   | 0   | 1          | 1   |

| 1   | 1   | 0          | 0   |

|   | Input | Out         | put          |

|---|-------|-------------|--------------|

| A | В     | LHS = (A.B) | RHS =A' + B' |

| 0 | 0     |             |              |

| 0 | 1     |             |              |

| 1 | 0     |             |              |

| 1 | 1     |             |              |

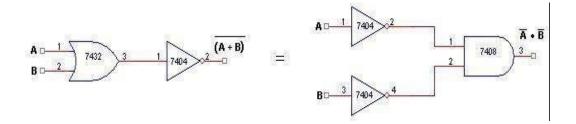

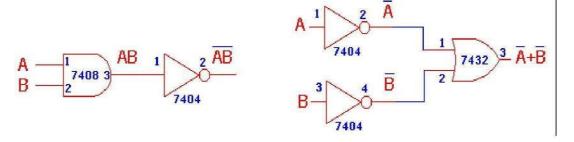

### Pin diagram for reference

- 1. Test the individual ICs with its specified verification table for proper working.

- 2. Connections are made as per the circuit/logic diagram.

- 3. Make sure that the ICs are enabled by giving the suitable Vcc and ground connections.

- 4. Apply the logic inputs to the appropriate terminals of the ICs.

- 5. Observe the logic output for the inputs applied.

- 6. Verify the observed logic output with the verification/truth table given.

### PRE LAB:

Basic Theorems:

- a) A+0 = A

- b) A\*1 = A

- a) A+1=1

- b) A\*0 = 0

- a) A+A=A

- b) A\*A = A

- a)  $A+\bar{A}=1$

- b)  $A*\bar{A} = 0$

### **Universal Gate:**

NAND and NOR are called universal gate, using this we can implement all other basic gates like AND, OR, NOT. One of the main disdvantages of using the complete sets of AND, OR and NOT gates is that to produce any equivalent logic gate or function we require two (or more) different types of logic gate, AND and NOT, or OR and NOT, or all three as shown above. However, we can realise all of the other Boolean functions and gates by using just one single type of universal logic gate, the NAND (NOT AND) or the NOR (NOT OR) gate, thereby reducing the number of different types of logic gates required, and also the cost.

### **POST LAB:**

- 1. What is the Truth table for function F = A + B'C?

- 2. How to implement AND using NAND?

- 3. How to implement AND using NOR?

### **RESULT:**

Thus verified the Boolean theorem using logic gates and it's the truth table

### Ex.No: 2 Design and implement Half/Full Adder and Subtractor

### AIM:

To design and construct half adder, full adder, half subtractor and full subtractor circuits and verify the truth table using logic gates.

#### THEORY:

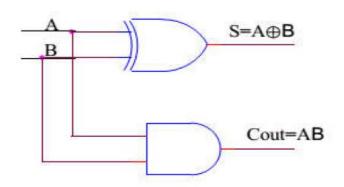

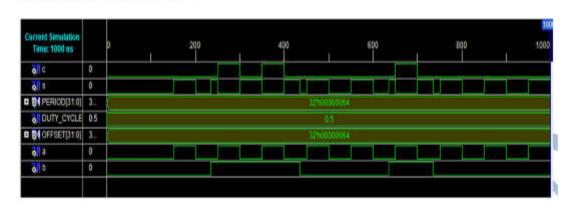

### **HALF ADDER:**

A half adder has two inputs for the two bits to be added and two outputs one from the sum 'S' and other from the carry 'c' into the higher adder position. Above circuit is called as a carry signal from the addition of the less significant bits sum from the X-OR Gate the carry out from the AND gate.

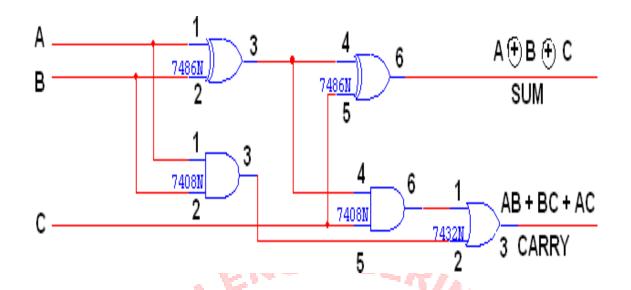

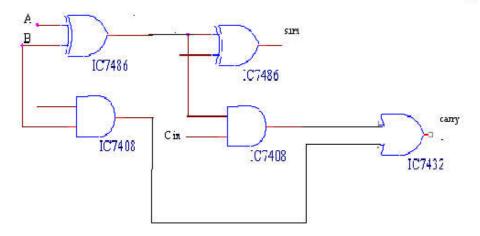

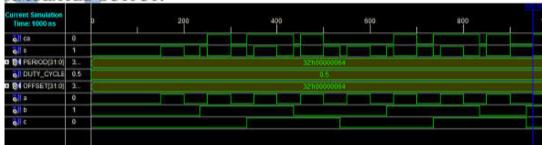

#### **FULL ADDER:**

A full adder is a combinational circuit that forms the arithmetic sum of input; it consists of three inputs and two outputs. A full adder is useful to add three bits at a time but a half adder cannot do so. In full adder sum output will be taken from X-OR Gate, carry output will be taken from OR Gate.

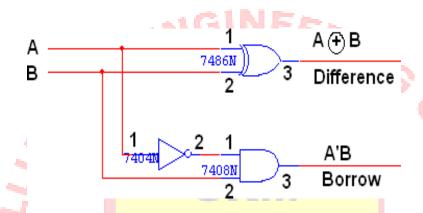

### HALF SUBTRACTOR:

The half subtractor is constructed using X-OR and AND Gate. The half subtractor has two input and two outputs. The outputs are difference and borrow. The difference can be applied using X-OR Gate, borrow output can be implemented using an AND Gate and an inverter.

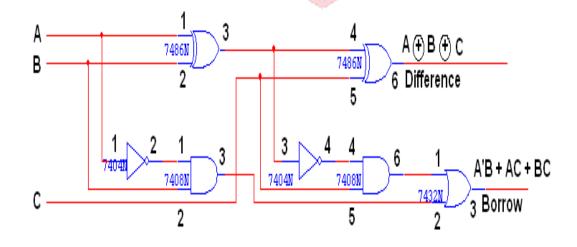

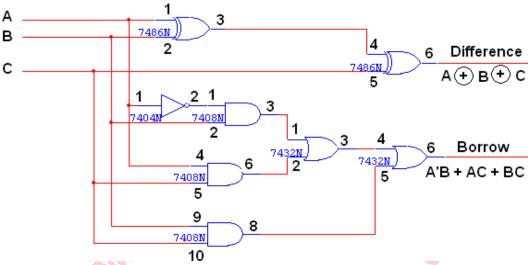

### **FULL SUBTRACTOR:**

The full subtractor is a combination of X-OR, AND, OR, NOT Gates. In a full subtractor the logic circuit should have three inputs and two outputs. The two half subtractor put together gives a full subtractor. The first half subtractor will be C and A B. The output will be difference output of full subtractor. The expression AB assembles the borrow output of the half subtractor and the second term is the inverted difference output of first X-OR.

### PRELAB:

### **K-MAP METHOD:**

The **Karnaugh map** (**KM** or **K-map**) is a method of simplifying Boolean algebra expressions The map method provides a simple, straight forward procedure for

minimizing Boolean functions. This method may be regarded as a pictorial form of truth table. This method is known as Karnaugh map or k-map. in Karnaugh maps, the cells are ordered in Gray code, [6][4] and each cell position represents one combination of input conditions, while each cell value represents the corresponding output value

### **APPLICATIONS:**

Karnaugh maps are used to simplify real-world logic requirements so that they can be implemented using a minimum number of physical logic gates. A sum-of-products expression can always be implemented using AND gates feeding into an OR gate, and a product-of-sums expression leads to OR gates feeding an AND gate. Karnaugh maps can also be used to simplify logic expressions in software design

CDM

### **APPARATUS REQUIRED:**

| Sl.No. | COMPONENT      | SPECIFICATION | QTY. |

|--------|----------------|---------------|------|

| 1.     | AND GATE       | IC 7408       | 1    |

| 2.     | X-OR GATE      | IC 7486       | 1    |

| 3.     | NOT GATE       | IC 7404       | 1    |

| 4.     | OR GATE        | IC 7432       | 1    |

| 3.     | IC TRAINER KIT |               | 1    |

| 4.     | PATCH CORDS    | -             | 23   |

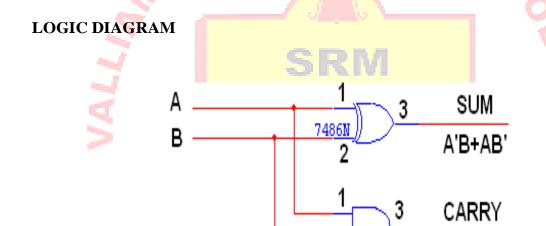

### **CIRCUIT DIAGRAM & TRUTH TABLE:**

a) HALF ADDER

### **TRUTH TABLE**

| A | В | CARR         | SU |

|---|---|--------------|----|

|   |   | $\mathbf{Y}$ | M  |

| 0 | 0 | 0            | 0  |

| 0 | 1 | 0            | 1  |

| 1 | 0 | 0            | 1  |

| 1 | 1 | 1            | 0  |

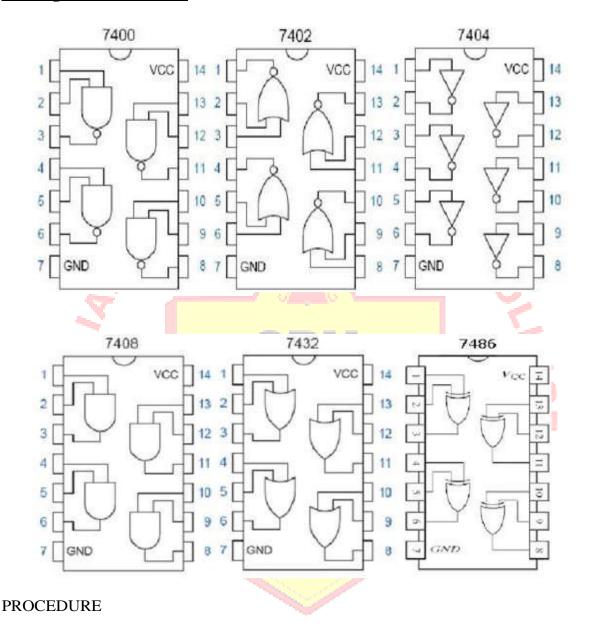

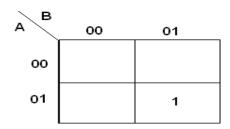

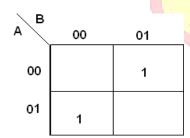

### K-Map for SUM

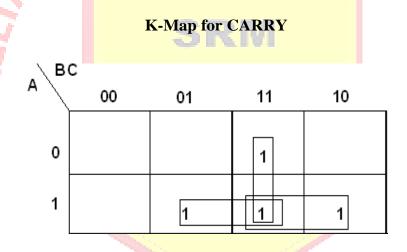

### K-Map for CARRY

AΒ

SUM = A'B + AB'

CARRY = AB

### b) FULL ADDER

### TRUTH TABLE

| A | В | С | CARR         | SU |

|---|---|---|--------------|----|

|   |   |   | $\mathbf{Y}$ | M  |

| 0 | 0 | 0 | 0            | 0  |

| 0 | 0 | 1 | 0            | 1  |

| 0 | 1 | 0 | 0            | 1  |

| 0 | 1 | 1 | 1            | 0  |

| 1 | 0 | 0 | 0            | 1  |

| 1 | 0 | 1 | 1            | 0  |

| 1 | 1 | 0 | 1            | 0  |

| 1 | 1 | 1 | 1            | 1  |

7408N

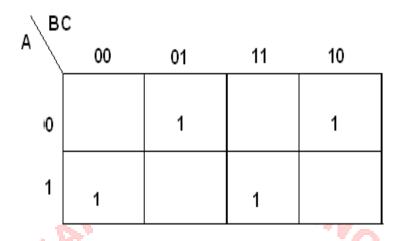

### K-Map for SUM

SUM = A'B'C + A'BC' + ABC' + ABC

CARRY = AB + BC + AC

**LOGIC DIAGRAM**

FULL ADDER USING TWO HALF ADDER

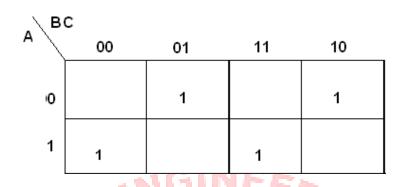

### HALF SUBTRACTOR

### TRUTH TABLE:

| A | В | BORROW | DIFFEREN | CE |

|---|---|--------|----------|----|

| 0 | 0 | 0      | 0        |    |

| 0 | 1 | 1      | 1        |    |

| 1 | 0 | 0      | 1        |    |

| 1 | 1 | 0      | 0        |    |

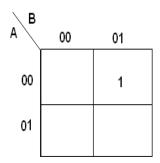

### K-Map for DIFFERENCE

DIFFERENCE = A'B + AB'

### K-Map for BORROW

BORROW = A'B

### **LOGIC DIAGRAM:**

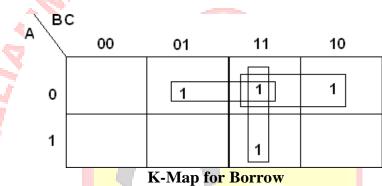

### **FULL SUBTRACTOR**

### TRUTH TABLE

| Α | В | C | BORRO | DIFFERENC |

|---|---|---|-------|-----------|

| A | 2 |   | W     | E         |

| 0 | 0 | 0 | 0     | 0         |

| 0 | 0 | 1 | 1     | 1         |

| 0 | 1 | 0 | 1     | 1         |

| 0 | 1 | 1 | 1     | 0         |

| 1 | 0 | 0 | 0     | 1         |

| 1 | 0 | 1 | 0     | 0         |

| 1 | 1 | 0 | 0     | 0         |

| 1 | 1 | 1 | 1     | 1         |

### **K-Map for Difference**

Difference = A'B'C + A'BC' + AB'C' + ABC

$$Borrow = A'B + BC + A'C$$

### FULL SUBTRACTOR USING TWO HALF SUBTRACTOR:

### **FULL SUBTRACTOR**

### **PROCEDURE**

- 1. Test the individual ICs with its specified verification table for proper working.

- 2. Connections are made as per the circuit/logic diagram.

- 3. Make sure that the ICs are enabled by giving the suitable Vcc and ground connections.

- 4. Apply the logic inputs to the appropriate terminals of the ICs.

- 5. Observe the logic output for the inputs applied.

### **POSTLAB:**

- 1. Derive the equation for Full Adder using two Half Adder?

- 2. Derive the equation for Full Subtractor using two Half Subtractor?

- 3. Simplify the Boolean function x(x'+y)

### Result

Thus design and implement of half/full adder and subtractor is done

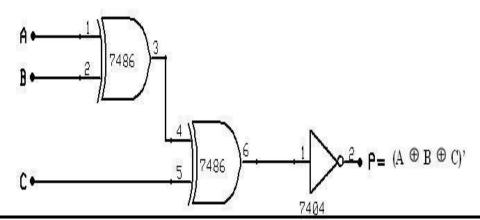

EX.NO 3: Design and implement combinational circuits using MSI devices-Parity generator / checker

### AIM:

To design and verify the truth table of a three bit Odd Parity generator and checker.

### **APPARATUS REQUIRED:**

| S.No | Name of the Apparatus  | Range   | Quantity    |

|------|------------------------|---------|-------------|

| 1.   | Digital IC trainer kit |         | 1           |

| 2.   | EX-OR gate             | IC 7486 |             |

| 3.   | NOT gate               | IC 7404 |             |

| 4.   | Connecting wires       | THERE.  | As required |

### THEORY:

A parity bit is used for the purpose of detecting errors during transmission of binary information. A parity bit is an extra bit included with a binary message to make the number of 1's either odd or even. The message including the parity bit is transmitted and then checked at the receiving end for errors. An error is detected if the checked parity does not correspond with the one transmitted. The circuit that generates the parity bit in the transmitter is called a parity generator and the circuit that checks the parity in the receiver is called a parity checker. In even parity the added parity bit will make the total number of 1's an even amount and in odd parity the added parity bit will make the total number of 1's an odd amount. In a three bit odd parity generator the three bits in the message together with the parity bit are transmitted to their destination, where they are applied to the parity checker circuit. The parity checker circuit checks for possible errors in the transmission. Since the information was transmitted with odd parity the four bits received must have an odd number of 1's, indicating that one bit has changed during transmission. The output of the parity checker is denoted by PEC (parity error check) and it will be equal to 1 if an error occurs, i.e., if the four bits received has an even number of 1's.

### **PRELAB:**

### **Advantages of Parity**

The advantages of parity are

• Simplicity

• Easy to use

### **Applications of Parity**

The applications of parity are

- In digital systems and many hardware applications, this parity is used

- The parity bit is also used in Small Computer System Interface (SCSI) and also in Peripheral Component Interconnect (PCI) to detect the errors

### **ODD PARITY GENERATOR:**

### **TRUTH TABLE:**

|   | S.No | (Thre | INPUT | ssage) | OUTPUT<br>( Odd Parity bit) |

|---|------|-------|-------|--------|-----------------------------|

|   | - 3  | A     | В     | C      | P                           |

| ſ | 1.   | 0     | 0     | 0      | 1                           |

| ſ | 2.   | 0     | 0     | 1      | 0                           |

| Ī | 3.   | 0     | 1     | 0      | 0                           |

| Ī | 4.   | 0     | 1     | 1      | RM                          |

| Į | 5.   | 1     | 0     | 0      | 0                           |

| I | 6.   | 1     | 0     | 1      | 1                           |

| ۱ | 7.   | 1     | 1 🔞   | 0      | 1                           |

| 1 | 8.   | 1     | 1     | 1      | 0                           |

From the truth table the expression for the output parity bit is,

$$P(A, B, C) = \Sigma (0, 3, 5, 6)$$

Also written as,

$$P = A'B'C' + A'BC + AB'C + ABC' = (A B C)$$

### **CIRCUIT DIAGRAM:**

### **ODD PARITY GENERATOR**

31

### **ODD PARITY CHECKER**

### **TRUTH TABLE:**

|      |       | INI                | PUT   |   | OUTPUT               |  |

|------|-------|--------------------|-------|---|----------------------|--|

| S.No | ( for | ( four bit message |       |   | (Parity error        |  |

|      |       | Rece               | ived) |   | check)               |  |

|      | A     | В                  | C     | P | X                    |  |

| 1.   | 0     | 0                  | 0     | 0 | 1                    |  |

| 2.   | 0     | 0                  | 0     | 1 | 0                    |  |

| 3.   | 0     | 0                  | 1     | 0 | 0                    |  |

| 4.   | 0     | 0                  | 1     | 1 | 1                    |  |

| 5.   | 0     | 1                  | 0     | 0 | $\Box$ 0 $\Xi$ $\Xi$ |  |

| 6.   | 0     | 1                  | 0     | 1 | 1                    |  |

| 7.   | 0     | 100                | 1     | 0 | 1                    |  |

| 8.   | 0     | 1                  | 1     | 1 | 0                    |  |

| 9.   | 1     | 0                  | 0     | 0 | 0                    |  |

| 10.  | 1     | 0                  | 0     | 1 | 1                    |  |

| 11.  | 1     | 0                  | 1     | 0 | / Jan 100 V          |  |

| 12.  | 1     | 0                  | 1     | 1 | 0                    |  |

| 13.  | 1     | 1                  | 0     | 0 | СБри                 |  |

| 14.  | 1     | 1                  | 0     | 1 | 0                    |  |

| 15.  | 1     | 1                  | 1     | 0 | 0                    |  |

| 16.  | 1     | 1                  | 1     | 1 | 1                    |  |

From the truth table the expression for the output parity checker bit is,  $X(A, B, C, P) = \Sigma(0, 3, 5, 6, 9, 10, 12, 15)$

The above expression is reduced as,

$$X = (A \quad B \quad C \quad P)$$

### **CIRCUIT DIAGRAM:**

### **ODD PARITY CHECKER**

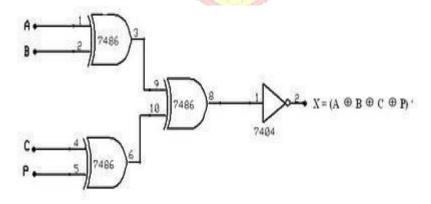

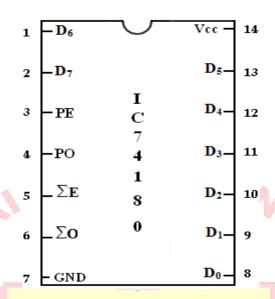

### **8- Bit ODD/EVEN PARITY GENERATOR/ CHECKER:**

### **PIN DIAGRAM**:

SRM

### **FUNCTION TABLE**:

| INPUTS                    |       |   | OUTPUTS |    |

|---------------------------|-------|---|---------|----|

| Number of Data<br>Inputs  | PE PO |   | ΣE      | ΣΟ |

| $({\bf D}_0 - {\bf D}_7)$ |       |   |         |    |

| EVEN                      | _1    | 0 | 1       | 0  |

| ODD                       | 1     | 0 | 0       | 1  |

| EVEN                      | 0     | 1 | 0       | 1  |

| ODD                       | 0     | 1 | 1       | 0  |

| X                         | 1     | 1 | 0       | 0  |

| X                         | 0     | 0 | 1       | 1  |

### **POSTLAB:**

- 1. Which OSI Layer takes care of error detection and correction?

- 2. Name the other two techniques to perform error detection and correction.

- 3. Discuss about generator and checker.

### **RESULT**

The design of the three bit odd Parity generator and checker circuits was done and their truth tables were verified.

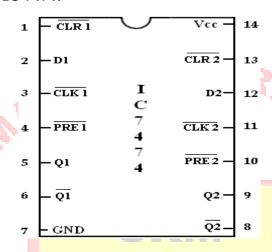

### EX.NO.4

### **Implementation of Shift Register**

#### AIM:

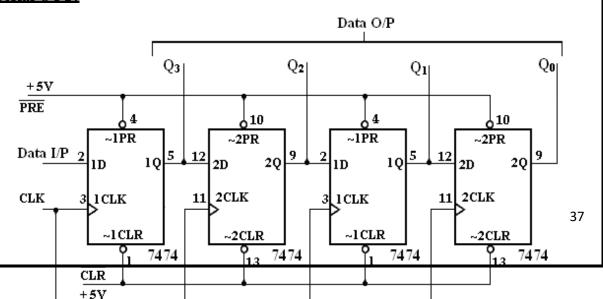

To implement and verify the truth table of Serial in serial Out(SISO), Serial in parallel Out(SIPO), Parallel in serial Out(PISO) & Parallel in parallel Out(PIPO)

# **APPARATUS REQUIRED:**

| S.No | Name of the Apparatus  | Range   | Quantity    |

|------|------------------------|---------|-------------|

| 1.   | Digital IC trainer kit |         | 1           |

| 2.   | D Flip Flop            | IC 7474 | 2           |

| 3.   | Connecting wires       | INEEN   | As required |

### THEORY:

A register capable of shifting its binary information either to the left or to the right is called a shift register. The logical configuration of a shift register consists of a chain of flip flops connected in cascade with the output of one flip flop connected to the input of the next flip flop. All the flip flops receive a common clock pulse which causes the shift from one stage to the next. The Q output of a D flip flop is connected to the D input of the flip flop to the left. Each clock pulse shifts the contents of the register one-bit position to the right. The serial input determines, what goes into the right most flip flop during the shift. The serial output is taken from the output of the left most flip flop prior to the application of a pulse. Although this register shifts its contents to its left, if we turn the page upside down we find that the register shifts its contents to the right. Thus a unidirectional shift register can function either as a shift right or a shift left register.

### **PRELAB:**

- 1. Flip flops can be used to store a single bit of binary data (1or 0). However, in order to store multiple bits of data, we need multiple flip flops. N flip flops are to be connected in an order to store n bits of data. A **Register** is a device which is used to store such information. It is a group of flip flops connected in series used to store multiple bits of data.

- 2. The information stored within these registers can be transferred with the help of **shift registers**. Shift Register is a group of flip flops used to store multiple bits of data.

- 3. Applications of shift register.

- ❖ The shift registers are used for temporary data storage.

- ❖ The shift registers are also used for data transfer and data manipulation.

- ❖ The serial-in serial-out and parallel-in parallel-out shift registers are used to produce time delay to digital circuits.

- ❖ The serial-in parallel-out shift register is used to convert serial data into parallel data thus they are used in communication lines where demultiplexing of a data line into several parallel line is required.

- ❖ A Parallel in Serial out shift register us used to convert parallel data to serial data.

### **PIN DIAGRAM OF IC 7474:**

# **Function Table:**

|        | Inputs |          |   |   |          |  |  |  |  |

|--------|--------|----------|---|---|----------|--|--|--|--|

| Preset | Clear  | Clock    | D | Q | Q'       |  |  |  |  |

| 0      | 1      | X        | X | 1 | 0        |  |  |  |  |

| 1      | 0      | X        | X | 0 | 1        |  |  |  |  |

| 0      | 0      | X        | X | 1 | 1        |  |  |  |  |

| 1      | 1      | <b>A</b> | 0 | 0 | 1        |  |  |  |  |

| 1      | 1      | <b>↑</b> | 1 | 1 | 0        |  |  |  |  |

| 1      | 1      | 0        | X | N | o Change |  |  |  |  |

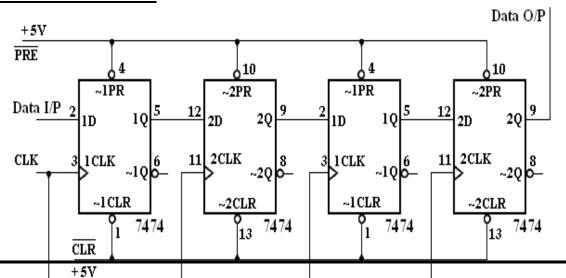

### **SERIAL IN SERIAL OUT:**

36

# **TABLE:**

| CL<br>K | Serial<br>IN | Serial<br>OUT |

|---------|--------------|---------------|

| 1       | 1            | 0             |

| 2       | 1            | 0             |

| 3       | 1            | 0             |

| 4       | $\sim 1$ M.  | 1             |

| 5       | 0            | EFD.          |

| 6       | 0            | 711/4         |

| 7       | 0            | 1 4           |

| 8       | 0            | 0             |

# **TRUTH TABLE:**

| CLK | DATA                  | OUTPU<br>T            |                |                |       |  |  |  |

|-----|-----------------------|-----------------------|----------------|----------------|-------|--|--|--|

|     |                       | <b>Q</b> <sub>3</sub> | $\mathbb{Q}_2$ | Q <sub>1</sub> | $Q_0$ |  |  |  |

| 1   | <b>S</b> <sup>1</sup> | 1                     | 0              | 0              | 0     |  |  |  |

| 2   | 0                     | 0                     | 7              | 0              | 0     |  |  |  |

| 3   | 0                     | 0                     | 0              | 1              | 0     |  |  |  |

| 4   | 1                     | 1                     | 0              | 0              | 1     |  |  |  |

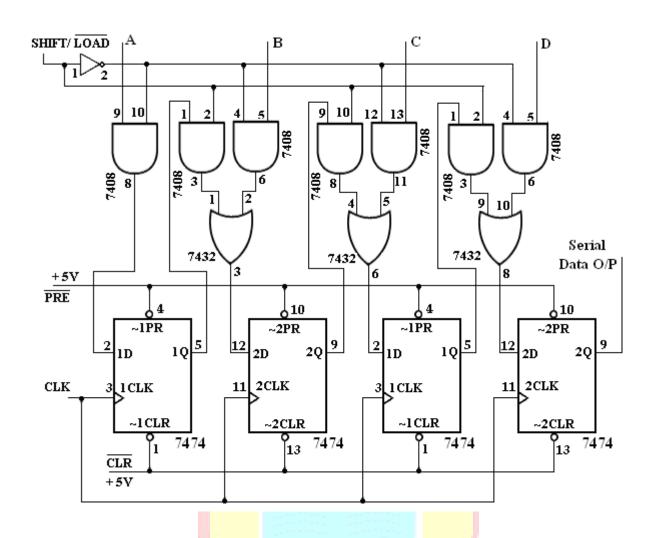

# Parallel IN Serial OUT:

# **LOGIC DIAGRAM:**

# **TRUTH TABLE:**

| S/L' | CLK |   | OUTPU<br>T |   |   |   |  |  |  |  |  |

|------|-----|---|------------|---|---|---|--|--|--|--|--|

|      |     | A | A B C D    |   |   |   |  |  |  |  |  |

| 0    | 0   | 1 | 0          | 0 | 1 | 1 |  |  |  |  |  |

| 1    | 1   | 1 | 0          | 0 | 1 | 0 |  |  |  |  |  |

| 1    | 2   | 1 | 0          | 0 | 1 | 0 |  |  |  |  |  |

| 1    | 3   | 1 | 0          | 0 | 1 | 1 |  |  |  |  |  |

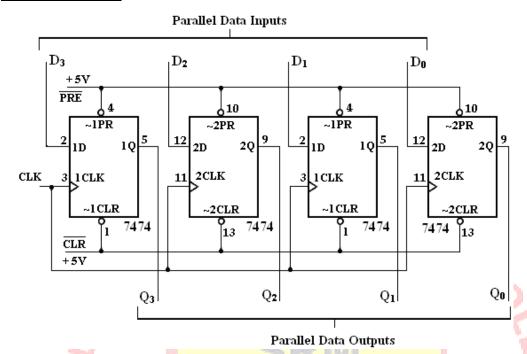

# **Parallel IN Parallel OUT:**

# Logic Diagram:

# **TRUTH TABLE:**

| CLK |                | DATA           | INPUTS         |                | OUTPU<br>T     |                |                |                |  |

|-----|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|--|

|     | $\mathbf{D}_3$ | $\mathbf{D}_2$ | $\mathbf{D}_1$ | $\mathbf{D}_0$ | $\mathbf{Q}_3$ | $\mathbf{Q}_2$ | $\mathbf{Q}_1$ | $\mathbf{Q}_0$ |  |

| 1   | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1              |  |

| 2   | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              |  |

### **PROCEDURE**:

- 1. Connections are given as per the logic diagram.

- 2. Logic inputs are given as per the logic diagram.

- 3. Observe the logic output and verify with the truth tables.

### **POSTLAB:**

- 1. Classify the types of Shift register.

- 2. Types of Flip flops and their truth table

- 3. Realize JK Flipflop using DFlip Flop.

### **RESULT:**

Thus the design and implementation of Serial in serial Out (SISO), Serial in parallel Out (SIPO), Parallel in serial Out (PISO), Parallel in parallel Out (PIPO) were done successfully.

#### Ex.No:05 Design and implementation of synchronous counters

#### AIM:

To design and implement synchronous counter.

2bit asynchronous counter

3 bit asynchronous counter

4 bit asynchronous counter

#### THEORY:

A register that goes through the prescribed sequence of states upon the application of input pulse is called counter. A counter that follows a binary number sequence is binary EERING counter. A n bit counter consists of n flip flop.

There are two types of counter

- i) Synchronous counter

- ii) Asynchronous counter

In synchronous counter common clock pulse trigger all flip flops at same time.

In synchronous counter clock pulse applied to all function flip flop. The decision whether output of flip flop is complemented is determined by J & K if J = K = 0 then no change in output if J = K = 1 then complemented.

The least significant bit always complemented Q with every pulse. A flip flop in any other positive complemented when LSB goes to 1. For (eg.) in 4 bit counter let the input  $A_3A_2A_1A_0 =$ 0111, then output will be 1000. Because A0 is always complemented. A<sub>1</sub> complemented since  $A_1A_0$  is 11 &  $A_2$  is complemented since  $A_2A_1A_0$  is 111. So next output is 1000.

### PRELAB:

# 1. Shift Register Vs Counter

A register is a memory device that can be used to store more than one bit of information and usually realized as several flip-flops with common control signals that control the movement of data to and from the register. The registers can hold data to be used for temporary storage or it can participate in arithmetic or logical operations.

A counter is a special case of a register. A counter is a register capable of incrementing and/or decrementing its contents, in other words a counter is a register that goes through a predetermined sequence of states.

# 2. Types of Counter

- Synchronous counter

- Asynchronous Counter or Ripple Counter

- Up/Down Counter

- Decade Counter

- Ring counter

- Cascaded counter

- Johnson counter

- Modulus counter

# SNOWEED.

# 3. Synchronous Vs Asynchronous counter

- ❖ Asynchronous (ripple) counter changing state bits are used as clocks to subsequent state flip-flops

- ❖ Synchronous counter all state bits change under control of a single clock

# **APPARATUS REQUIRED:**

# SRM

| S.NO | COMPONENET                   | SPECIFICATION | QUANTITY |

|------|------------------------------|---------------|----------|

| 1.   | JK- Fl <mark>ip Flop</mark>  | IC 7476       | 2        |

| 2.   | AND <mark>GATE</mark>        | IC7408        | 1        |

| 3.   | IC TRAI <mark>NER KIT</mark> | 50            | 1        |

| 4.   | BATCH <mark>CARDS</mark>     |               | 34       |

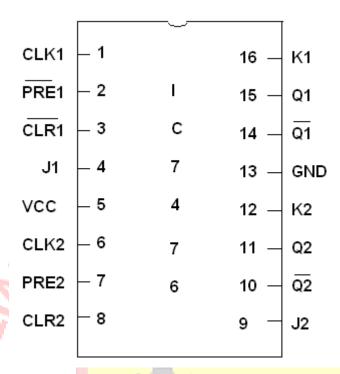

# PIN CONFIGURATION OF IC 7476 (JK FLIP FLOP):

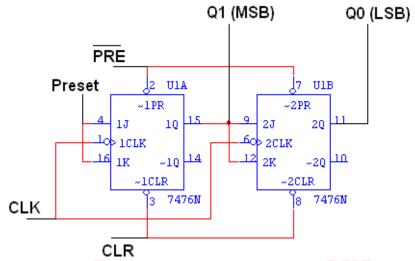

# 2-BIT SYNCHRONOUS COUNTER:

# **STATE TABLE:**

| Present | State | N | lext Sta | ate        | Inj | puts |

|---------|-------|---|----------|------------|-----|------|

| Q1      | Q0    | ( | Q1 (     | <b>Q</b> 0 | I1  | 10   |

| 0       | 0     |   | 0        | 1          | 0   | 1    |

| 0       | 1     |   | 1        | 0          | 1   | 1    |

| 1       | 0     |   | 1        | 1          | 0   | 1    |

| 1       | 1     | ( | 0        | 0          | 1   | 1    |

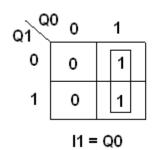

# K-MAP:

# **LOGIC DIAGRAM:**

# SYNCHRONOUS COUNTER:

# **STATE TABLE:**

|   | Present State |    |     | Ne | xt St | ate |           | Inputs | 5  |

|---|---------------|----|-----|----|-------|-----|-----------|--------|----|

|   | ~             |    |     |    |       |     |           |        |    |

|   | Q2            | Q1 | Q0  | Q2 | Q1    | Q0  | <b>T2</b> | T1     | Т0 |

| 4 | 0             | 0  | 0   | 0  | 0     | 1   | 0         | 0      | 1  |

|   | 0             | 0  | 1   | 0  | 4     | 0   | 0         | 1      | 1  |

| P | 0             | 1  | 0   | 0  | 1     | 1   | 0         | 0      | 1  |

|   | 0             | 1  | 1 ( | 1  | 0     | 0   | 1         | 1      | 1  |

|   | 1             | 0  | 0   | 1  | 0     | 1   | 0         | 0      | 1  |

|   | 1             | 0  | 1   | 1  | 1     | 0   | 0         | 1      | 1  |

|   | 1             | 1  | 0   | 1  | 1     | 1   | 0         | 0      | 1  |

|   | 1             | 1  | 1   | 0  | 0     | 0   | 1         | 1      | 1  |

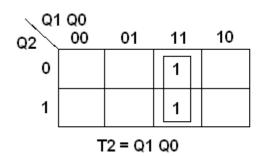

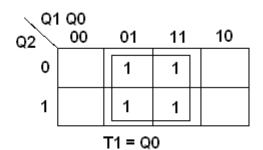

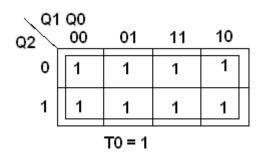

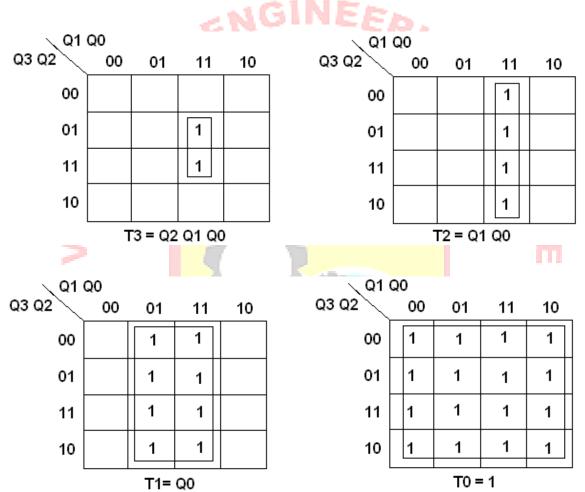

### K-MAP:

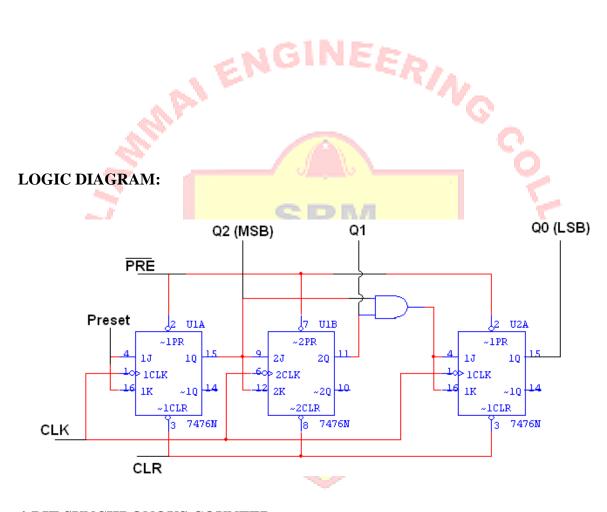

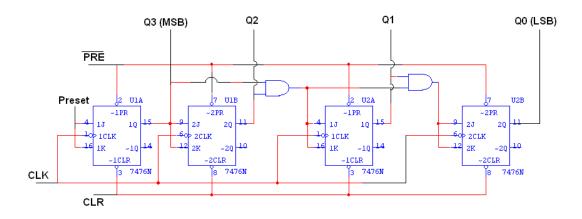

**4-BIT SYNCHRONOUS COUNTER:**

**LOGIC DIAGRAM:**

# K-MAP:

# **STATE TABLE:**

| Present State | Next State Inputs |             |  |

|---------------|-------------------|-------------|--|

| Q3 Q2 Q1 Q0   | Q3 Q2 Q1 Q0       | T3 T2 T1 T0 |  |

| 0       0       0       0       0       0       0       0       0       0       1       0       0       0       1       1       0       0       0       1       1       0       0       0       1       1       1       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                        |   |   |    |   |   |   |   |     |     |      |   |   |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----|---|---|---|---|-----|-----|------|---|---|------|

| 0         0         1         1         0         0         0         1         1         0         0         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                    | 0 | 0 | 0  | 0 |   | 0 | 0 | 0   | 1   | 0    | 0 | 0 | 1    |

| 0       0       1       1       0       1       0       0       1       1       1         0       1       0       0       0       1       0       0       0       1       1         0       1       0       1       1       1       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td></td> <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>1</td>      | 0 | 0 | 0  | 1 |   | 0 | 0 | 1   | 0   | 0    | 0 | 1 | 1    |

| 0       1       0       0       0       1       0       0       0       0       1         0       1       0       1       1       0       0       0       1       1         0       1       1       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td></td> <td>0</td> <td>0</td> <td>1</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>1</td>      | 0 | 0 | 1  | 0 |   | 0 | 0 | 1   | 1   | 0    | 0 | 0 | 1    |

| 0       1       0       1       1       0       0       0       1       1         0       1       1       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                              | 0 | 0 | 1  | 1 |   | 0 | 1 | 0   | 0   | 0    | 1 | 1 | 1    |

| 0       1       1       0       0       0       1       1       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                        | 0 | 1 | 0  | 0 |   | 0 | 1 | 0   | 1   | 0    | 0 | 0 | 1    |

| 0       1       1       1       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                        | 0 | 1 | 0  | 1 |   | 0 | 1 | 1   | 0   | 0    | 0 | 1 | 1    |

| 1       0       0       0       1       0       0       0       1         1       0       0       1       1       0       0       0       1       1         1       0       1       0       1       1       1       0       0       0       1       1       1         1       1       0       0       1       1       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 </td <td>0</td> <td>1</td> <td>1</td> <td>0</td> <td></td> <td>0</td> <td>M</td> <td>31</td> <td>VE/</td> <td>E.P.</td> <td>0</td> <td>0</td> <td>1</td> | 0 | 1 | 1  | 0 |   | 0 | M | 31  | VE/ | E.P. | 0 | 0 | 1    |

| 1       0       0       1       1       0       0       0       1       1         1       0       1       0       1       1       0       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                              | 0 | 1 | 1  | 1 | 7 | 1 | 0 | 0   | 0   | 1    | 1 | 1 | 1    |

| 1       0       1       0       1       1       0       0       0       1         1       0       1       1       1       0       0       0       1       1       1         1       1       0       0       1       1       0       0       0       1       1         1       1       0       1       1       1       1       1       1       1       1       0       0       0       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 | 0 | 0  | 0 |   | 1 | 0 | 0   | 1   | 0    | 0 | 0 | 1    |

| 1       0       1       1       1       0       0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1                                                                                                                                        | 1 | 0 | 0  | 1 |   | 1 | 0 | 1   | 0   | 0    | 0 | 1 |      |

| 1     1     0     0     1     1     0     0     0     1       1     1     0     1     1     1     0     0     0     1     1       1     1     1     1     1     1     1     1     0     0     0     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1 | 0 | j  | 0 |   | 1 | 0 | 21  | 1   | 0    | 0 | 0 | 1    |

| 1     1     0     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1     1 <td>1</td> <td>0</td> <td>[1</td> <td>1</td> <td></td> <td>1</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>1</td> <td>1(1)</td>                                                                                                                            | 1 | 0 | [1 | 1 |   | 1 | 1 | 0   | 0   | 0    | 1 | 1 | 1(1) |

| 1 1 1 0 1 1 1 0 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1 | 1 | 0  | 0 |   | 1 | 1 | 0   | 1   | 0    | 0 | 0 | 1    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 | 1 | 0  | 1 |   | 1 | 1 | _1  | 0   | 0    | 0 | 1 | 1    |

| 1 1 1 1 0 0 0 0 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1 | 1 | 1  | 0 | V | 1 | 1 | _1_ | -1  | 0    | 0 | 0 | 1    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 | 1 | 1  | 1 |   | 0 | 0 | 0   | 0   | 1    | 1 | 1 | 1    |

# **PROCEDURE:**

- (i) Connections are given as per the circuit diagram.

- (ii) Give the logic input as per the truth table.

- (iii) Observe the logical outputs and verify the truth table.

# **POSTLAB:**

- 1. How many Flip Flops are required to design MOD 35 Counter?

- 2. How many states are there in a 3bit ring counter?

- 3. Depict the excitation table of the following flip flop

- JK FlipFlop

- DFlipFlop

- T Flip Flop

- 4. What is the use of characteristics table and excitation table of flip flops?

# **RESULT:**

Thus the design and implement of synchronous counter was designed and output was verified.

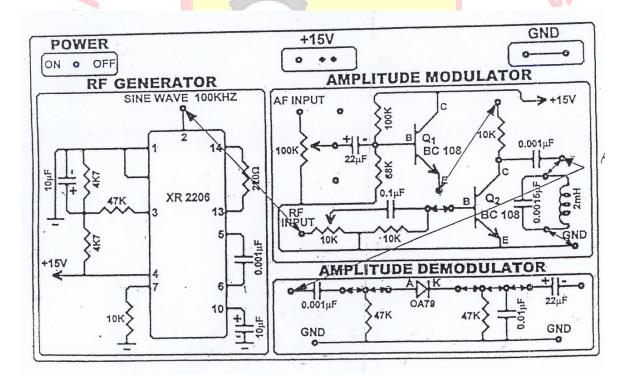

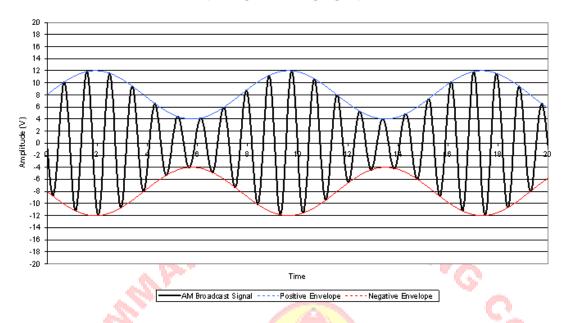

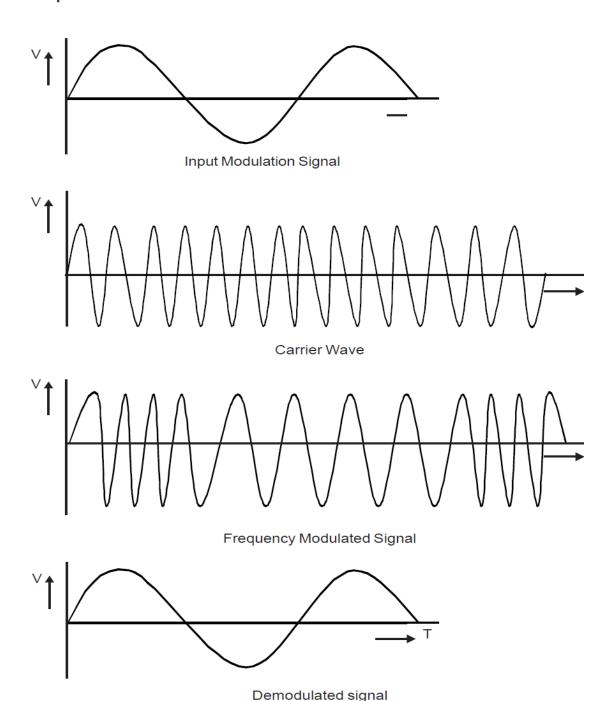

# **EX.NO6** Amplitude Modulation and Demodulation

### Aim:

1. To generate amplitude modulated wave and determine the percentage modulation. \

ENGINEERIN

2. To Demodulate the modulated wave using envelope detector.

# **Apparatus Required:**

- 1. Amplitude Modulation and Demodulation Trainer

- 2. Function Generator

- 3. Oscilloscope

- **4.** Connecting Wires

# Theory:

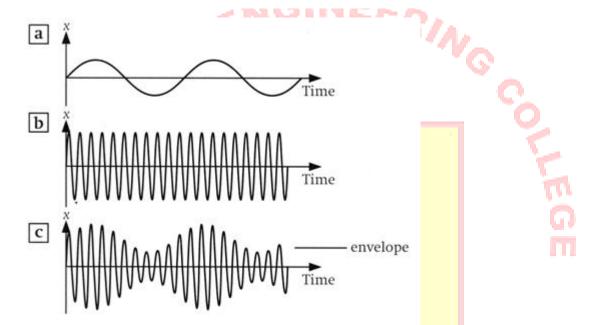

Modulation is defined as the process by which some characteristics of a carrier signal is varied in accordance with a modulating signal. The base band signal is referred to as the modulating signal and the output of the modulation process is called as the modulation signal.

Amplitude modulation is defined as the process in which is the amplitude of the carrier wave is varied about a means values linearly with the base band signal. The envelope of the modulating wave has the same shape as the base band signal provided the following two requirements are satisfied

- (1). the carrier frequency fc must be much greater then the highest frequency components fm of the message signal m (t)

- i.e.  $fc \gg fm$

- (2) The modulation index must be less than unity. if the modulation index is greater than unity, the carrier wave becomes over modulated

### **PRELAB:**

- 1. Need for Modulation in the communication systems

- \* Reduction in the height of antenna

- **❖** Avoids mixing of signals

- ❖ Increases the range of communication

- Multiplexing is possible

- Improves quality of reception

- 2. Frequency range of human voice signal range becomes

300Hz to 3000Hz

3. AM spectrum consists of Carrier frequency with both upper and lower sideband

### **Procedure:**

- 1 Switch on the trainer and check the O/P of carrier generator with (RF generator) with oscilloscope and observe the values

- 2. Connect 1KHz with 2 Volts A.F signal at AF I/P to the modulator circuit with function generator and Observe the value.

- 3. Connect the carrier signal(RF) at carrier I/P(RF) of modulator circuit.

- 4. Observe the modulator output signal at AM O/P observe the values.

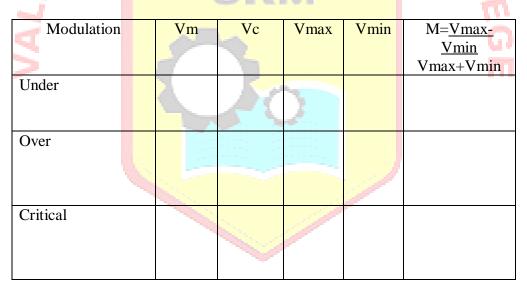

- 5. Vary the modulating frequency and amplitude and observe the effects on the modulated waveform. Observe the critical modulation ,over modulation and under modulation forms.

- 6. The depth of modulation can be varied using the variable knob (potentiometer) provided at A.F. input.

- 7. The percentage of modulation or modulation factor can be calculated using the following formulas.

- 10. Connect the AM wave to the demodulator circuit and observe the output

- 11. Note down frequency and amplitude of the demodulated output waveform.

# 12. Draw the demodulated wave form., m=1

# Tabulation 1:

| Waveform         | Amplitude | Time Period | Frequency |

|------------------|-----------|-------------|-----------|

| Unit             | V         | ms          | Hz        |

| Message Signal   |           |             |           |