# SRM VALLIAMMAI ENGINEERING COLLEGE

(An Autonomous Institution)

SRM NAGAR, KATTANKULATHUR-603203

## DEPARTMENT OF ELECTRICAL AND ELECTRONICS ENGINEERING

#### LAB MANUAL

#### 1905507 -MICROPROCESSORS AND MICROCONTROLLERS LABORATORY

#### **V SEMESTER**

(Academic Year – 2022-2023-ODD sem)

Prepared By

Mrs. S. Vanila, A.P. (Sel.G) / EEE

0042

#### **SYLLABUS**

#### **OBJECTIVES:**

- ➤ To perform simple arithmetic operations using assembly language program and study the addressing modes & instruction set of 8085 & 8051.

- > To develop skills in simple program writing in assembly languages.

- > To write an assembly language program to convert Analog input to Digital output and Digital input to Analog output.

- > To perform interfacing experiments with μP8085 and μC8051.

- > To study various digital integrated circuits used in simple system configuration.

#### LIST OF EXPERIMENTS

|            | Programming exercises / Experiments with μP8085:                                      |

|------------|---------------------------------------------------------------------------------------|

| 1.         | Simple arithmetic operations: Multi precision addition / subtraction/multiplication / |

|            | division.                                                                             |

| 2.         | Programming with control instructions: Increment / Decrement, Ascending Descending    |

|            | order, Maximum / Minimum of numbers, Rotate instructions, Hex /ASCII / BCD code       |

|            | conversions.                                                                          |

| <b>3.</b>  | Interface Experiments:                                                                |

|            | A/D Interfacing.                                                                      |

|            | D/A Interfacing.                                                                      |

|            | Traffic light controller.                                                             |

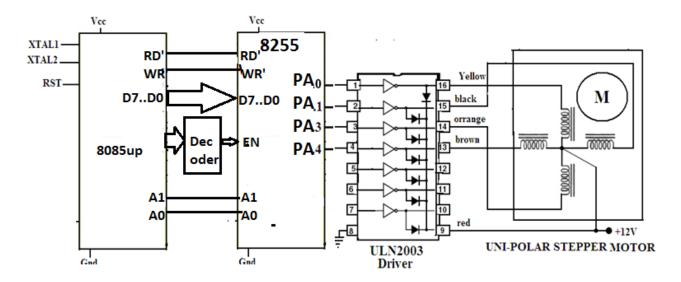

| 4.         | Stepper motor controller interface.                                                   |

|            | Programming exercises / Experiments with μC8051:                                      |

| <b>5.</b>  | Simple arithmetic operations with 8051: Multi precision addition / subtraction        |

|            | /multiplication / division.                                                           |

| 6.         | Programming with control instructions: Increment / Decrement, Ascending               |

|            | /Descending order, Maximum / Minimum of numbers, Rotate instructions, Hex /ASCII      |

|            | / BCD code conversions.                                                               |

| 7.         | Interface Experiments:                                                                |

|            | A/D Interfacing.                                                                      |

|            | D/A Interfacing.                                                                      |

|            | Traffic light controller                                                              |

| 8.         | Stepper motor controller interface.                                                   |

|            | Experiments with Digital ICs:                                                         |

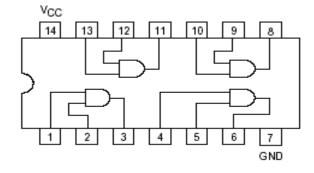

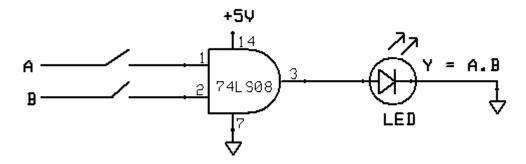

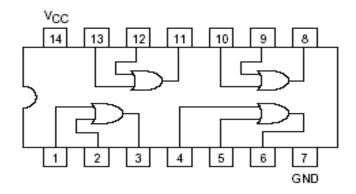

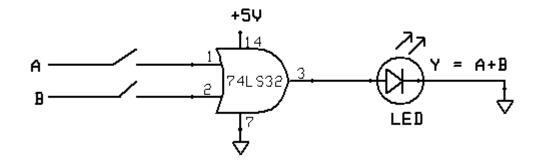

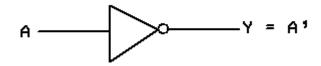

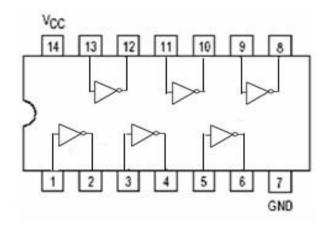

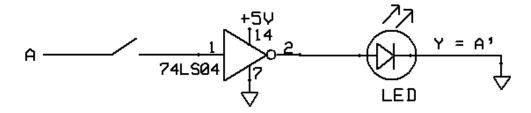

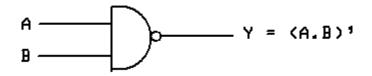

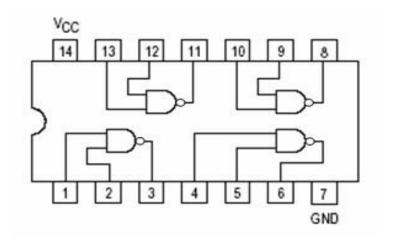

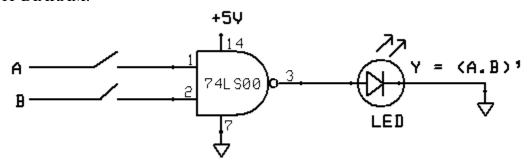

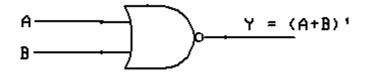

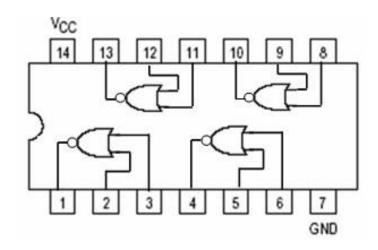

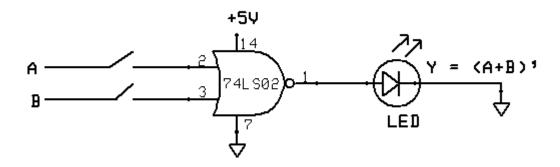

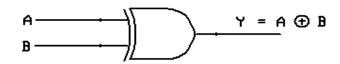

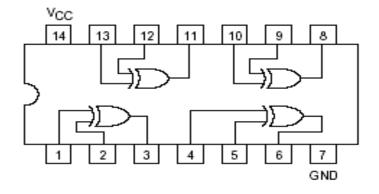

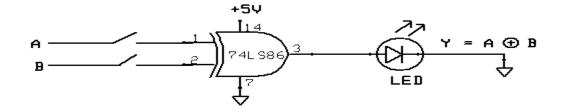

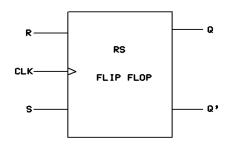

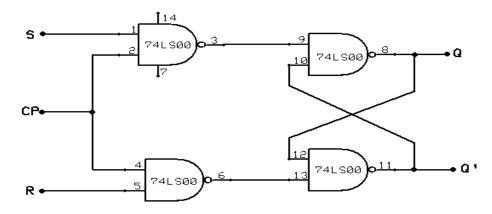

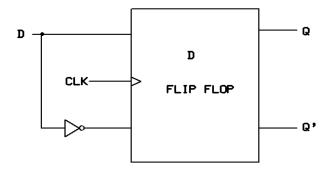

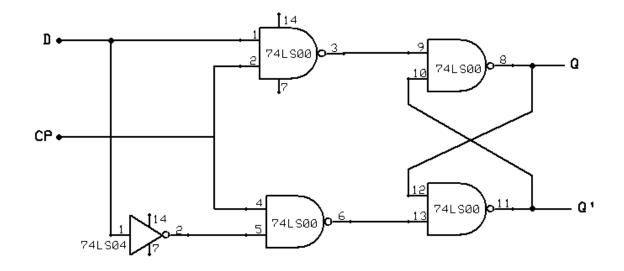

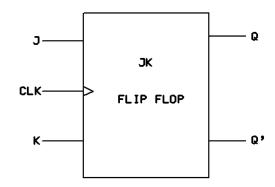

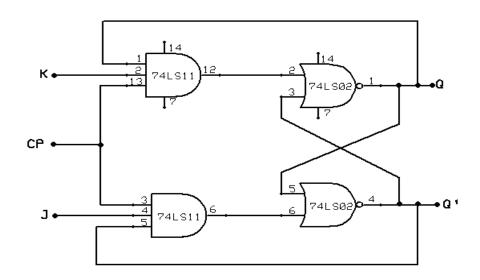

| 9.         | Study of Basic Digital IC's.(Verification of truth table for AND, OR, EXOR, NOT,      |

|            | NOR, NAND, JK FF, RS,FF, D FF)                                                        |

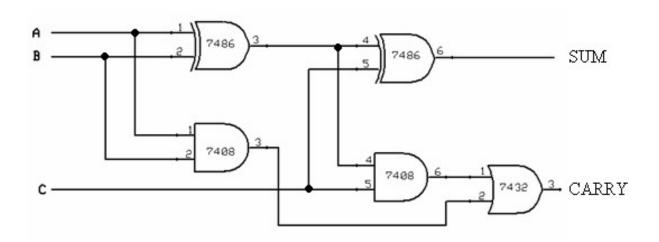

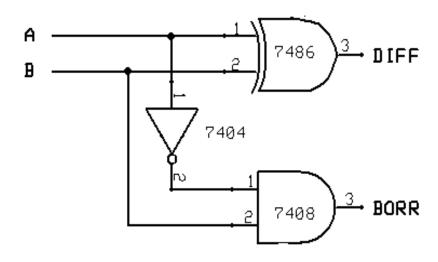

| 10.        | Implementation of Boolean Functions, Adder/ Subtractor circuits; Realizing            |

|            | given function with minimum number of gates by minimization methods.                  |

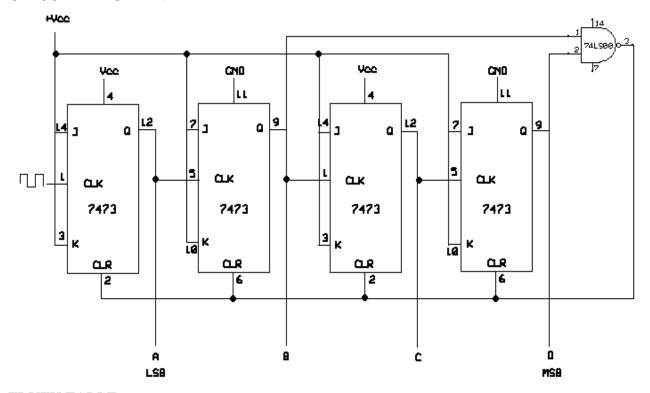

| 11.        | Study of binary / BCD counters, modulo-n counters.                                    |

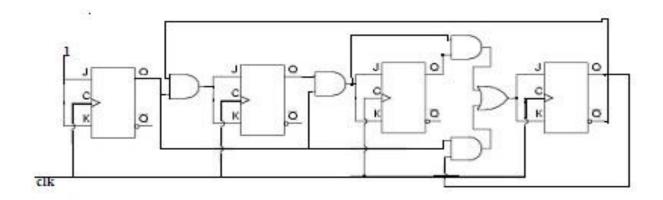

| <b>12.</b> | Design and implementation of Synchronous sequential counters.                         |

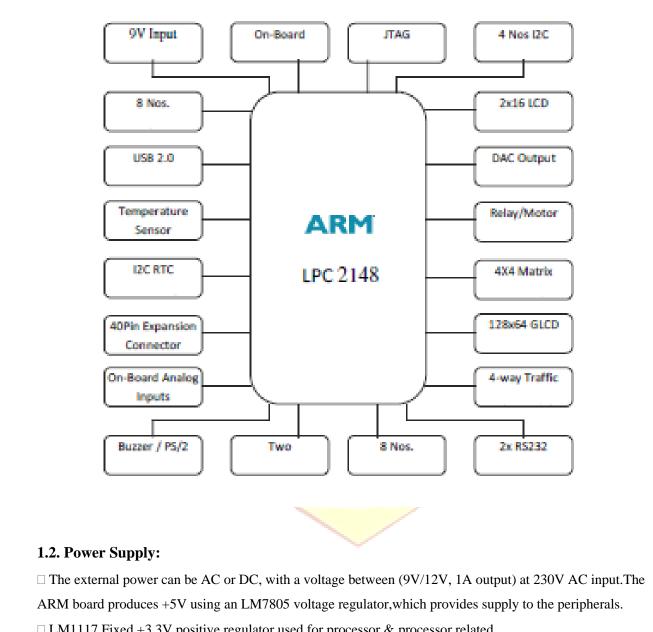

| 13.        | Programming ARM architecture with software tools.                                     |

## **CONTENTS**

| S. NO. | EXPERIMENT NAME                                                                                                                                 | PAGE<br>NO. |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|        | 8085 Experiments                                                                                                                                | •           |

| 1A     | 8 bit data addition                                                                                                                             |             |

| 1B     | 8 bit data subtraction                                                                                                                          |             |

| 1C     | 8 bit data multiplication                                                                                                                       |             |

| 1D     | 8 bit data divison                                                                                                                              |             |

| 2A     | Largest element in an array                                                                                                                     |             |

| 2B     | Smallest element in an array                                                                                                                    |             |

| 2C     | Sorting an array of data in Ascending order                                                                                                     |             |

| 2D     | Sorting an array of data in Descending order                                                                                                    |             |

| 2E     | Decimal to Hexadecimal conversion                                                                                                               |             |

| 2F     | Hexadecimal to decimal conversion                                                                                                               |             |

| 2G     | Hexa decimal TO ASCII conversion                                                                                                                |             |

| 2H     | ASCII to Hexa decimal conversion                                                                                                                |             |

| 3A     | Traffic light controller - Interfacing 8255 with 8085                                                                                           |             |

| 3B     | Interfacing Analog to Digital converter 8085 microprocessor                                                                                     |             |

| 3C     | Interfacing Digital to Analog converter 8085 microprocessor                                                                                     |             |

| 4      | Stepper motor controller interface                                                                                                              |             |

|        | 8051 Experiments                                                                                                                                |             |

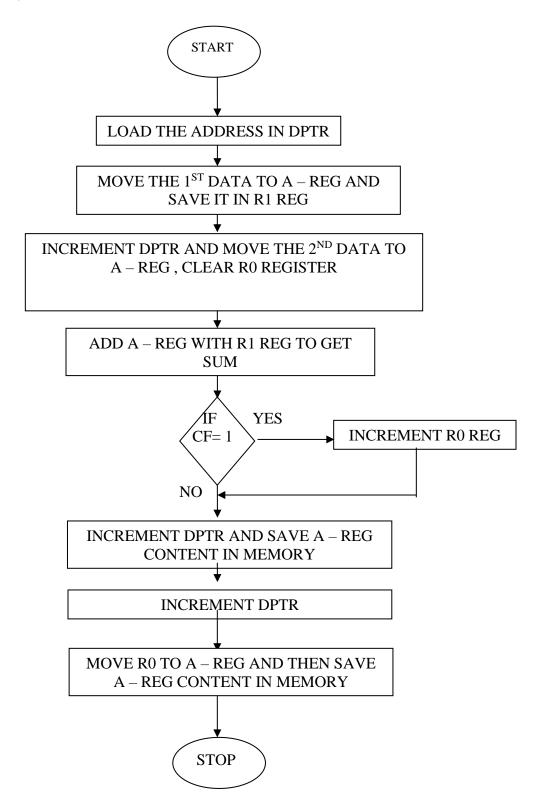

| 5A     | 8 bit data addition                                                                                                                             |             |

| 5B     | 8 bit data subtraction                                                                                                                          |             |

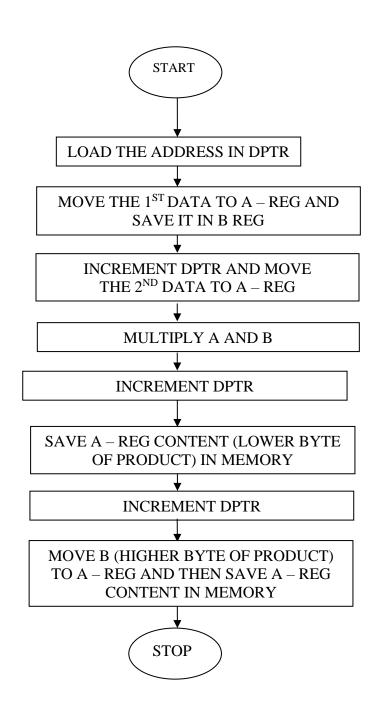

| 5C     | 8 bit data multiplication                                                                                                                       |             |

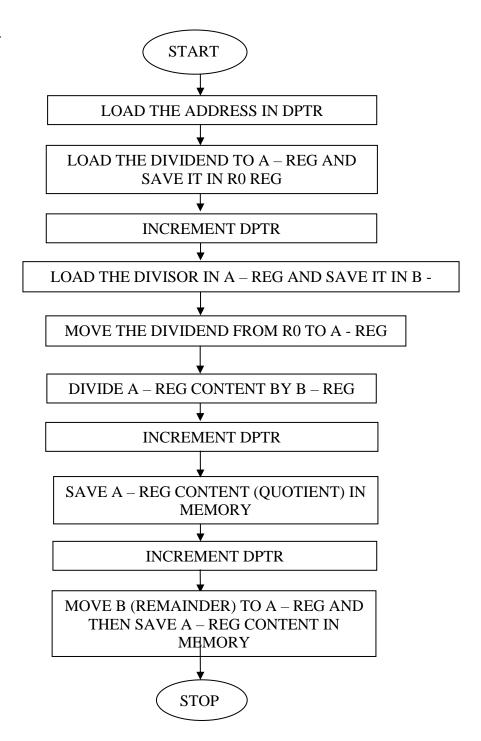

| 5D     | 8 bit data divison                                                                                                                              |             |

| 6A     | Largest element in an array                                                                                                                     |             |

| 6B     | Smallest element in an array                                                                                                                    |             |

| 6C     | ASCII to Hexa decimal conversion                                                                                                                |             |

| 7A     | Interfacing A/D and D/A converter with 8051 microcontroller                                                                                     |             |

| 7B     | Traffic light controller - Interfacing with 8051                                                                                                |             |

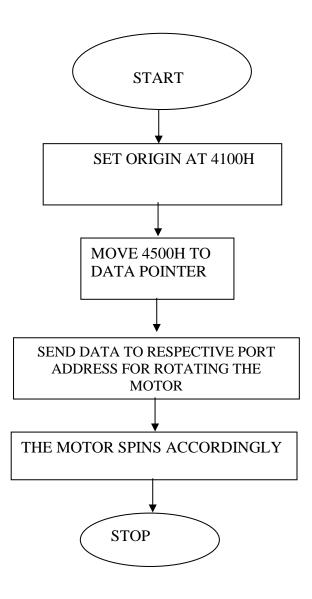

| 8      | Interfacing stepper motor with 8051 microcontroller                                                                                             |             |

|        | Experiments with Digital ICs                                                                                                                    | T           |

| 9      | Study of Basic Digital IC's. (Verification of truth table for AND, OR, EXOR, NOT, NOR, NAND, JK FF, RS, FF, D FF)                               |             |

| 10     | Implementation of Boolean Functions, Adder/ Subtractor circuits; Realizing given function with minimum number of gates by minimization methods. |             |

| 11     | Study of binary / BCD counters, modulo-n counters                                                                                               |             |

| 12     | Design and implementation of Synchronous sequential counters.                                                                                   |             |

| 13     | Programming ARM architecture with software tools.                                                                                               |             |

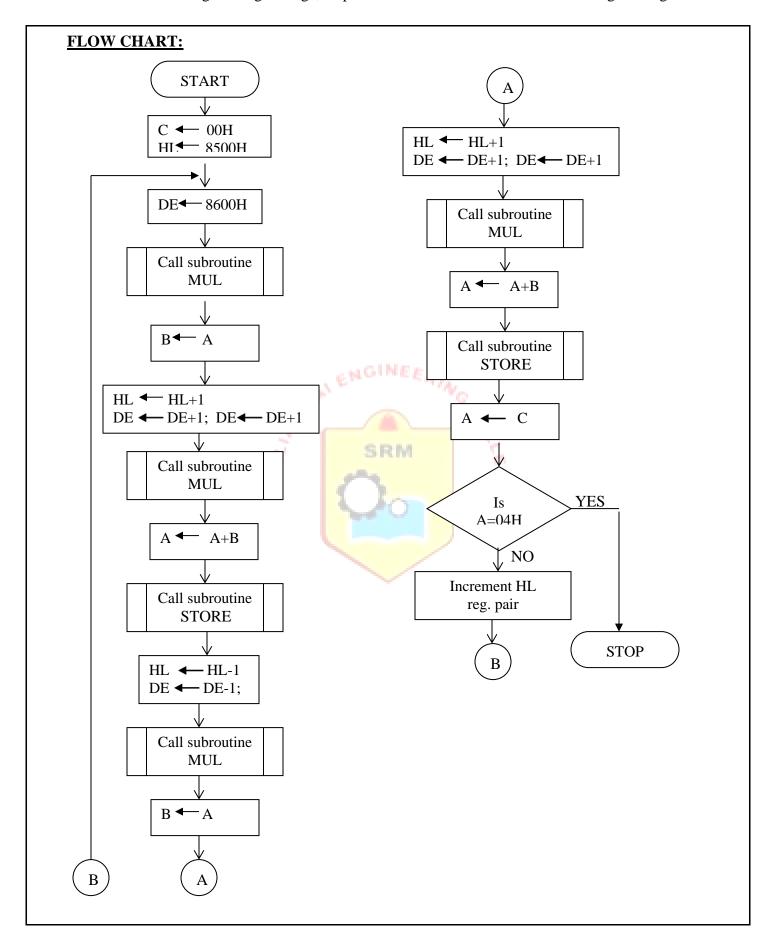

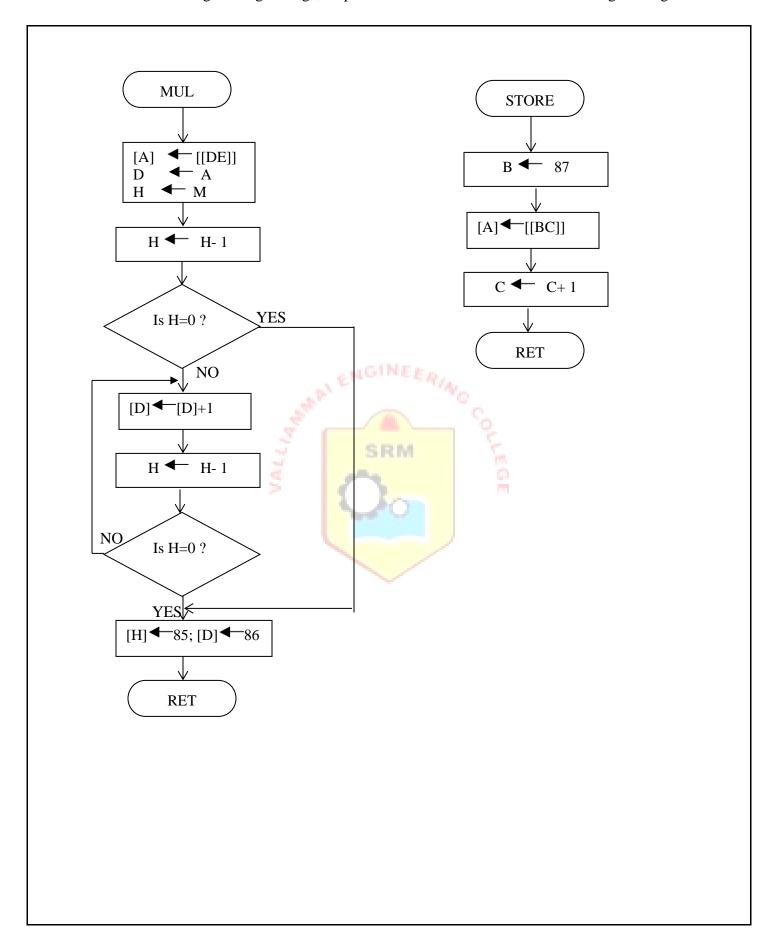

|        | ADDITIONAL EXPERIMENTS                                                                                                                          | <u>I</u>    |

| 14     | Programs to verify timer and interrupts in 8051 Microcontroller                                                                                 |             |

| 15     | 2x2 matrix multiplication                                                                                                                       |             |

|        | 1                                                                                                                                               |             |

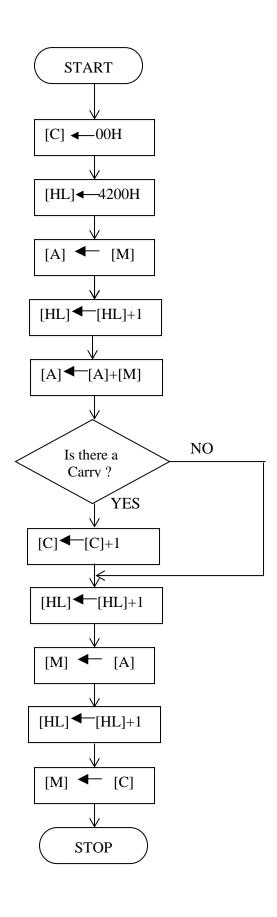

#### **FLOW CHART:**

#### 1(A) 8-BIT DATA ADDITION

#### AIM:

To add two 8 bit numbers stored at consecutive memory locations and also to verify the result.

#### **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board

- 1. Initialize memory pointer to data location.

- 2. Get the first number from memory in accumulator.

- 3. Get the second number and add it to the accumulator.

- 4. Store the answer at another memory location.

| ADDRESS | OPCODE | LABEL | MNEMONICS | OPERAND | COMMENT                               |

|---------|--------|-------|-----------|---------|---------------------------------------|

|         | OPCODE |       |           |         |                                       |

| 4100    |        | START | MVI       | C, 00   | Clear C reg.                          |

| 4101    |        |       |           |         |                                       |

| 4102    |        |       | LXI       | H, 4200 | Initialize HL reg. to                 |

| 4103    |        |       |           |         | 4500                                  |

| 4104    |        |       |           |         |                                       |

| 4105    |        |       | MOV       | A, M    | Transfer first data to                |

|         |        |       |           |         | accumulator                           |

| 4106    |        |       | INX       | Н       | Increment HL reg. to                  |

|         |        |       |           |         | point next memory                     |

|         |        |       |           |         | Location.                             |

| 4107    |        |       | ADD       | M       | Add first number to                   |

|         |        |       |           |         | acc. Content.                         |

| 4108    |        |       | JNC       | L1      | Jump to location if                   |

| 4109    |        |       |           |         | result does not yield                 |

| 410A    |        |       |           |         | carry.                                |

| 410B    |        |       | INR       | С       | Increment C reg.                      |

| 410C    |        | L1    | INX       | H       | Increment HL reg. to                  |

| 1100    |        | 21    | 11.77     | 11      | point next memory                     |

|         |        |       |           |         | Location.                             |

| 410D    |        |       | MOV       | M, A    | Transfer the result from              |

| 4100    |        |       | IVIO V    | IVI, A  |                                       |

| 410E    |        |       | INX       | Н       | acc. to memory.  Increment HL reg. to |

| 410E    |        |       | IINA      | п       | point next memory                     |

|         |        |       |           |         | 1 -                                   |

| 4100    |        |       | MOV       | MC      | Location.                             |

| 410F    |        |       | MOV       | M, C    | Move carry to memory                  |

| 4110    |        |       | HLT       |         | Stop the program                      |

| INI  | PUT | 0    | UTPUT |

|------|-----|------|-------|

| 4200 | 40  | 4202 | 60    |

| 4201 |     |      | 00    |

#### **RESULT:**

Thus the two 8 bit numbers stored at 4200 & 4201 are added and the result is stored at 4202 & 4203.

#### **VIVA QUESTIONS:**

- 1. What is the function of LXI H, 4000 H instruction?

- 2. How you can store a data in a memory location?

- 3. What is the meaning of INX

- 3. How you can read a data from a memory location?

- 4. What are flags available in 8085?

- 5. What is the function of RESET key of a 8085 microprocessor kit

- 6. What is the function of JNC instruction?

- 7. What is the difference between conditional and unconditional jump instruction?

- 8. What is multi byte?

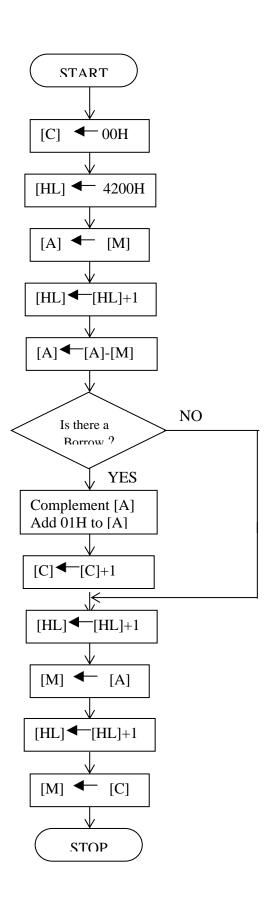

#### **FLOW CHART:**

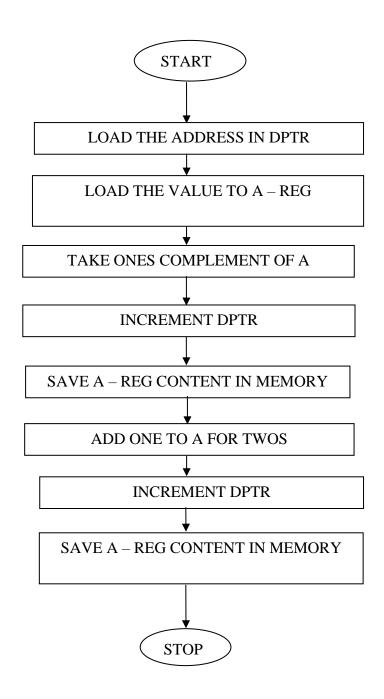

#### **1(B)** 8-BIT DATA SUBTRACTION

#### AIM:

To subtract two 8 bit numbers stored at consecutive memory locations and also to verify the result.

#### **APPARATUS REQUIRED:**

8085 microprocessor kit, key board

- 1. Initialize memory pointer to data location.

- 2. Get the first number from memory in accumulator.

- 3. Get the second number and subtract from the accumulator.

- 4. If the result yields a borrow, the content of the acc. is complemented and 01H is added to it (2's complement). A register is cleared and the content of that reg. is incremented in case there is a borrow. If there is no borrow the content of the acc. is directly taken as the result.

- 5. Store the answer at next memory location.

| ADDRESS | OPCODE | LABEL | MNEMONICS | OPERAND | COMMENT                                        |

|---------|--------|-------|-----------|---------|------------------------------------------------|

| 4100    |        | START | MVI       | C, 00   | Clear C reg.                                   |

| 4102    |        |       |           |         |                                                |

| 4102    |        |       | LXI       | H, 4200 | Initialize HL reg. to                          |

| 4103    |        |       |           |         | 4500                                           |

| 4104    |        |       |           |         |                                                |

| 4105    |        |       | MOV       | A, M    | Transfer first data to accumulator             |

| 4106    |        |       | INX       | Н       | Increment HL reg. to point next mem. Location. |

| 4107    |        |       | SUB       | M       | Subtract first number from acc. Content.       |

| 4108    |        |       | JNC       | L1      | Jump to location if                            |

| 4109    |        |       |           |         | result does not yield                          |

| 410A    |        |       |           |         | borrow.                                        |

| 410B    |        |       | INR       | С       | Increment C reg.                               |

| 410C    |        |       | CMA       |         | Complement the Acc. Content                    |

| 410D    |        |       | ADI       | 01H     | Add 01H to content of                          |

| 410E    |        |       |           |         | acc.                                           |

| 410F    |        | L1    | INX       | Н       | Increment HL reg. to point next mem. Location. |

| 4110    |        |       | MOV       | M, A    | Transfer the result from acc. to memory.       |

| 4111    |        |       | INX       | Н       | Increment HL reg. to point next mem. Location. |

| 4112    |        |       | MOV       | M, C    | Move carry to mem.                             |

| 4113    |        |       | HLT       |         | Stop the program                               |

| IN   | PUT     | 0    | UTPUT |

|------|---------|------|-------|

| 4200 | 4200 04 |      | 03    |

| 4201 | 01      | 4203 | 00    |

#### **RESULT:**

Thus the 8 bit numbers stored at 4200 &4201 are subtracted and the result is stored at 4202 & 4203.

#### **VIVA QUESTIONS:**

- 1. What is meant by ADI instruction

- 2. What is an instruction?

- 3. What is Mnemonic?

- 4. What is the purpose of CMA instruction?

- 5. What is the function of stack pointer?

- 6. Why ADI 01H is used in two's complement of an 8-bit number.

- 7. How many memory locations can be addressed by a microprocessor with 14 address lines?

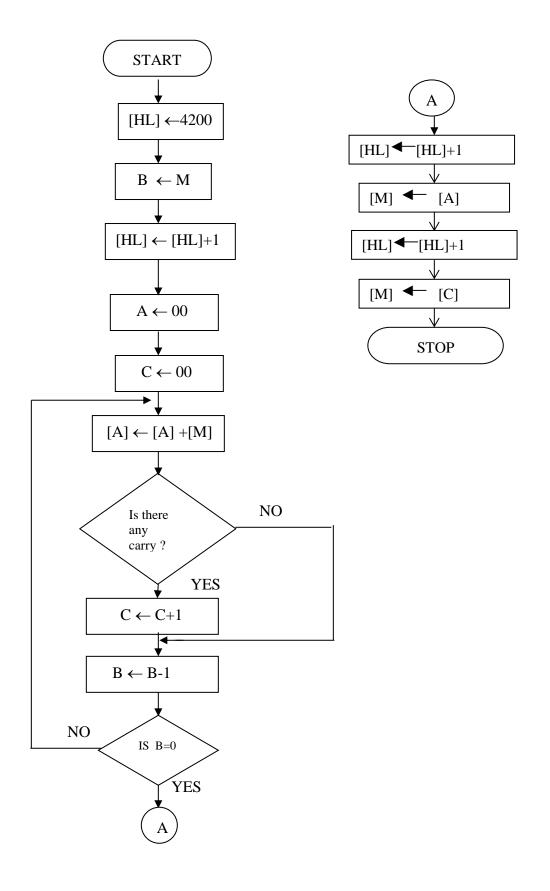

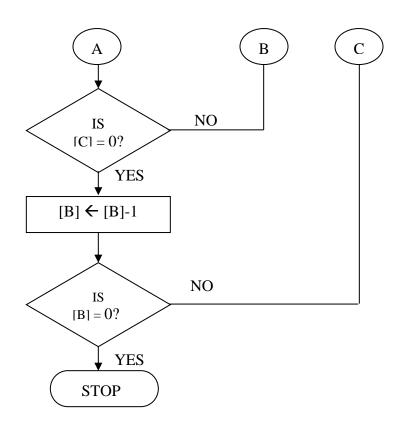

#### **FLOW CHART:**

#### 1(C) 8-BIT DATA MULTIPLICATION

#### AIM:

#### **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board

- 1. Initialize memory pointer to data location.

- 2. Move multiplicand to a register.

- 3. Move the multiplier to another register.

- 4. Clear the accumulator.

- 5. Add multiplicand to accumulator

- 6. Decrement multiplier

- 7. Repeat step 5 till multiplier comes to zero.

- 8. The result, which is in the accumulator, is stored in a memory location.

| ADDRESS | OPCODE | LABEL | MNEMONICS | OPERAND | COMMENT                                        |

|---------|--------|-------|-----------|---------|------------------------------------------------|

| 4100    |        | START | LXI       | H, 4200 | Initialize HL reg. to                          |

| 4101    |        |       |           |         | 4500                                           |

| 4102    |        |       |           |         |                                                |

| 4103    |        |       | MOV       | B, M    | Transfer first data to reg. B                  |

| 4104    |        |       | INX       | Н       | Increment HL reg. to point next mem. Location. |

| 4105    |        |       | MVI       | A, 00H  | Clear the acc.                                 |

| 4106    |        |       |           |         |                                                |

| 4107    |        |       | MVI       | C, 00H  | Clear C reg for carry                          |

| 4108    |        |       |           |         |                                                |

| 4109    |        | L1    | ADD       | M       | Add multiplicand multiplier times.             |

| 410A    |        |       | JNC       | NEXT    | Jump to NEXT if there                          |

| 410B    |        |       |           |         | is no carry                                    |

| 410C    |        |       |           |         |                                                |

| 410D    |        |       | INR       | С       | Increment C reg                                |

| 410E    |        | NEXT  | DCR       | В       | Decrement B reg                                |

| 410F    |        |       | JNZ       | L1      | Jump to L1 if B is not                         |

| 4110    |        |       |           |         | zero.                                          |

| 4111    |        |       |           |         |                                                |

| 4112    |        |       | INX       | Н       | Increment HL reg. to point next mem. Location. |

| 4113    |        |       | MOV       | M, A    | Transfer the result from acc. to memory.       |

| 4114    |        |       | INX       | Н       | Increment HL reg. to point next mem. Location. |

| 4115    |        |       | MOV       | M, C    | Transfer the result from C reg. to memory.     |

| 4116    |        |       | HLT       |         | Stop the program                               |

| IN   | PUT | 0    | UTPUT |

|------|-----|------|-------|

| 4200 | 02  | 4202 | 08    |

| 4201 | 04  | 4203 | 00    |

#### **RESULT:**

Thus the 8-bit multiplication was done in  $8085\mu p$  using repeated addition method and also the result is verified.

#### **VIVA QUESTION:**

- 1. Define two's complement of an 8-bit numbers.

- 2. What is meant by instruction ADC M?

- 3. What is the use of the instruction MOV A,M

- 4. What is the function of program counter?

- 5. Mention the types of 8085 instruction set.

- 6. How will you perform multiplication using ADD instruction?

- 7. Describe about DAD B instruction.

- 8. What is the purpose of the instruction MOV M,A

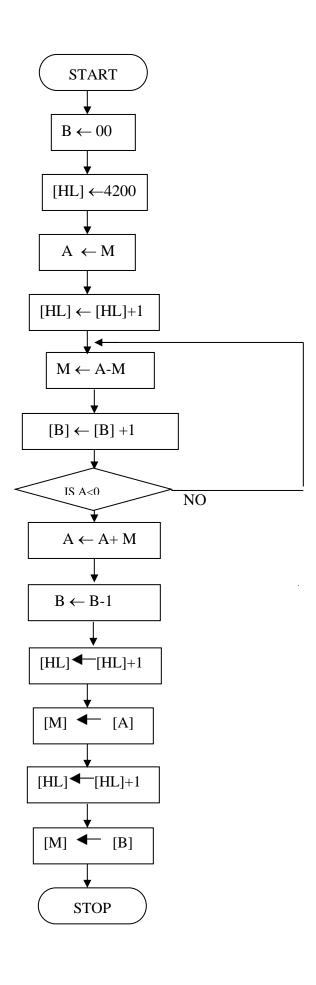

#### **FLOWCHART:**

#### 1(D) 8-BIT DIVISION

#### AIM:

To divide two 8-bit numbers stored in memory and also to verify the result.

#### **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board

- 1. Load Divisor and Dividend.

- 2. Subtract divisor from dividend.

- 3. Count the number of times of subtraction which equals the quotient.

- 4. Stop subtraction when the dividend is less than the divisor .The dividend now becomes the remainder. Otherwise go to step 2.

- 5. Stop the program execution.

| ADDRESS | OPCODE | LABEL | MNEMONICS | OPERAN<br>D | COMMENTS                                       |

|---------|--------|-------|-----------|-------------|------------------------------------------------|

| 4100    |        |       | MVI       | B,00        | Clear B reg for quotient                       |

| 4101    |        |       |           |             |                                                |

| 4102    |        |       | LXI       | H,4200      | Initialize HL reg. to                          |

| 4103    |        |       |           |             | 4200H                                          |

| 4104    |        |       |           |             |                                                |

| 4105    |        |       | MOV       | A,M         | Transfer dividend to acc.                      |

| 4106    |        |       | INX       | Н           | Increment HL reg. to point next mem. Location. |

| 4107    |        | LOOP  | SUB       | M           | Subtract divisor from dividend                 |

| 4108    |        |       | INR       | В           | Increment B reg                                |

| 4109    |        |       | JNC       | LOOP        | Jump to LOOP if result                         |

| 410A    |        |       |           |             | does not yield borrow                          |

| 410B    |        |       |           |             |                                                |

| 410C    |        |       | ADD       | M           | Add divisor to acc.                            |

| 410D    |        |       | DCR       | В           | Decrement B reg                                |

| 410E    |        |       | INX       | Н           | Increment HL reg. to point next mem. Location. |

| 410F    |        |       | MOV       | M,A         | Transfer the remainder from acc. to memory.    |

| 4110    |        |       | INX       | Н           | Increment HL reg. to point next mem. Location. |

| 4111    |        |       | MOV       | М,В         | Transfer the quotient from B reg. to memory.   |

| 4112    |        |       | HLT       |             | Stop the program                               |

| INI     | PUT  | OUT     | <b>TPUT</b> |

|---------|------|---------|-------------|

| ADDRESS | DATA | ADDRESS | DATA        |

| 4200    | 06   | 4202    | 00          |

| 4201    | 02   | 4203    | 03          |

#### **RESULT:**

Thus an ALP was written for 8-bit division and also the result is also verified.

#### **VIVA QUESTIONS:**

- 1. What SUB M instruction will do?

- 2. Describe SBB M instruction

- 3. Express the use of SUI with an example

- 4. Where SBI can be used?

- 5. Give the purpose of the instruction LDAX D

- 6. How will you perform Division using ADD instruction?

- 7. What is the need of ALE signal in 8085?

- 8. What are the addressing modes of 8085?

- 9. List the interrupt signals of 8085?

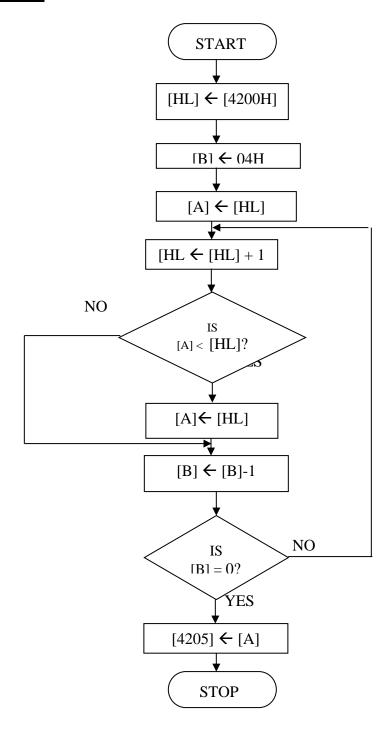

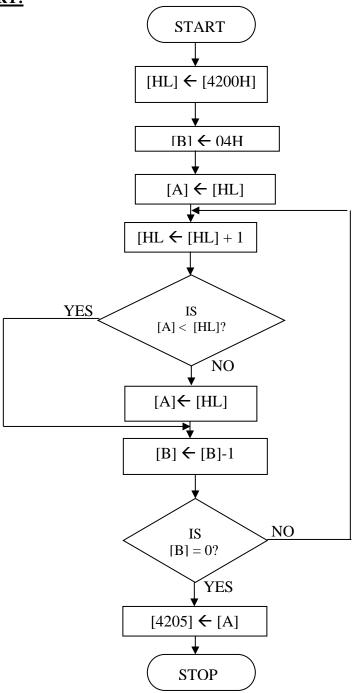

#### **FLOW CHART:**

#### **2(A)** LARGEST ELEMENT IN AN ARRAY

#### **AIM:**

To find the largest element in an array of data stored in memory and also to verify the result.

#### **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board

- 1. Place all the elements of an array in the consecutive memory locations.

- 2. Fetch the first element from the memory location and load it in the accumulator.

- 3. Initialize a counter (register) with the total number of elements in an array.

- 4. Decrement the counter by 1.

- 5. Increment the memory pointer to point to the next element.

- 6. Compare the accumulator content with the memory content (next element).

- 7. If the accumulator content is smaller, then move the memory content (largest element) to the accumulator. Else continue.

- 8. Decrement the counter by 1.

- 9. Repeat steps 5 to 8 until the counter reaches zero

- 10. Store the result (accumulator content) in the specified memory location.

| ADDRESS | OPCODE | LABEL | MNEMONICS | OPERAND | COMMENTS                    |

|---------|--------|-------|-----------|---------|-----------------------------|

| 4100    |        |       | LXI       | H,4200  | Initialize HL reg. to       |

| 4101    |        |       |           |         | 8100H                       |

| 4102    |        |       |           |         |                             |

| 4103    |        |       | MVI       | B,04    | Initialize B reg with no.   |

| 4104    |        |       |           |         | of comparisons(n-1)         |

| 4105    |        |       | MOV       | A,M     | Transfer first data to acc. |

| 4106    |        | LOOP1 | INX       | Н       | Increment HL reg. to        |

|         |        |       |           |         | point next memory           |

|         |        |       |           |         | location                    |

| 4107    |        |       | CMP       | M       | Compare M & A               |

| 4108    |        |       | JNC       | LOOP    | If A is greater than M      |

| 4109    |        |       |           |         | then go to loop             |

| 410A    |        |       |           |         |                             |

| 410B    |        |       | MOV       | A,M     | Transfer data from M to     |

|         |        |       |           |         | A reg                       |

| 410C    |        | LOOP  | DCR       | В       | Decrement B reg             |

| 410D    |        |       | JNZ       | LOOP1   | If B is not Zero go to      |

| 410E    |        |       |           |         | loop1                       |

| 410F    |        |       |           |         |                             |

| 4110    |        |       | STA       | 4205    | Store the result in a       |

| 4111    |        |       |           |         | memory location.            |

| 4112    |        |       |           |         |                             |

| 4113    |        |       | HLT       |         | Stop the program            |

| INP     | UT   | OUT     | PUT  |

|---------|------|---------|------|

| ADDRESS | DATA | ADDRESS | DATA |

| 4200    | 01   | 4205    | 07   |

| 4201    | 06   |         |      |

| 4202    | 03   |         |      |

| 4203    | 07   |         |      |

| 4204    | 02   |         |      |

#### **RESULT:**

Thus the largest number in the given array is found and it is stored at location 4205.

#### **VIVA QUESTIONS:**

- 1. What is meant by the instruction CMP M

- 2. What the instruction JNZ will do

- 3. State the logic behind the finding of largest element

- 4. List out the similarities b/w the CALL-RET and PUSH-POP instructions?

- 5. What is the need of ALE signal in 8085?

- 6. What are the addressing modes of 8085?

#### **FLOW CHART:**

#### **2(B) SMALLEST ELEMENT IN AN ARRAY**

#### AIM:

To find the smallest element in an array of data stored in memory and also to verify the result.

#### **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board

- 1. Place all the elements of an array in the consecutive memory locations.

- 2. Fetch the first element from the memory location and load it in the accumulator.

- 3. Initialize a counter (register) with the total number of elements in an array.

- 4. Decrement the counter by 1.

- 5. Increment the memory pointer to point to the next element.

- 6. Compare the accumulator content with the memory content (next element).

- 7. If the accumulator content is smaller, then move the memory content (largest element) to the accumulator. Else continue.

- 8. Decrement the counter by 1.

- 9. Repeat steps 5 to 8 until the counter reaches zero

- 10. Store the result (accumulator content) in the specified memory location.

| ADDRE | OPCODE | LABEL | MNEMONICS | OPERAND | COMMENTS                      |  |

|-------|--------|-------|-----------|---------|-------------------------------|--|

| SS    |        |       |           |         |                               |  |

| 4100  |        |       | LXI       | H,4200  | Initialize HL reg. to         |  |

| 4101  |        |       |           |         | 8100H                         |  |

| 4102  |        |       |           |         |                               |  |

| 4103  |        |       | MVI       | B,04    | Initialize B reg with no. of  |  |

| 4104  |        |       |           |         | comparisons(n-1)              |  |

| 4105  |        |       | MOV       | A,M     | Transfer first data to acc.   |  |

| 4106  |        | LOOP1 | INX       | Н       | Increment HL reg. to point    |  |

|       |        |       |           |         | next memory location          |  |

| 4107  |        |       | CMP       | M       | Compare M & A                 |  |

| 4108  |        |       | JC        | LOOP    | If A is lesser than M then go |  |

| 4109  |        |       |           |         | to loop                       |  |

| 410A  |        |       |           |         |                               |  |

| 410B  |        |       | MOV       | A,M     | Transfer data from M to A     |  |

|       |        |       |           |         | reg                           |  |

| 410C  |        | LOOP  | DCR       | В       | Decrement B reg               |  |

| 410D  |        |       | JNZ       | LOOP1   | If B is not Zero go to loop1  |  |

| 410E  |        |       |           |         |                               |  |

| 410F  |        |       |           |         |                               |  |

| 4110  |        |       | STA       | 4205    | Store the result in a memory  |  |

| 4111  |        |       |           |         | location.                     |  |

| 4112  |        |       |           |         |                               |  |

| 4113  |        |       | HLT       |         | Stop the program              |  |

| INPU    | T    | OUTPUT  |      |  |

|---------|------|---------|------|--|

| ADDRESS | DATA | ADDRESS | DATA |  |

| 4200    | 01   | 4205    | 01   |  |

| 4201    | 06   |         |      |  |

| 4202    | 03   |         |      |  |

| 4203    | 07   |         |      |  |

| 4204    | 02   |         |      |  |

#### **RESULT:**

Thus the smallest number in the given array is found and it is stored at location 4205.

#### **VIVA QUESTION:**

- 1. What is meant by instruction JC?

- 2. Tell about the instruction SHLD.

- 3. Summarize the instruction STAX B.

- 4. State the logic behind the finding of smallest element .

- 5. Why address bus is unidirectional?

- 6. List few instructions to clear accumulator?

- 7. What is the function of NOP instruction?

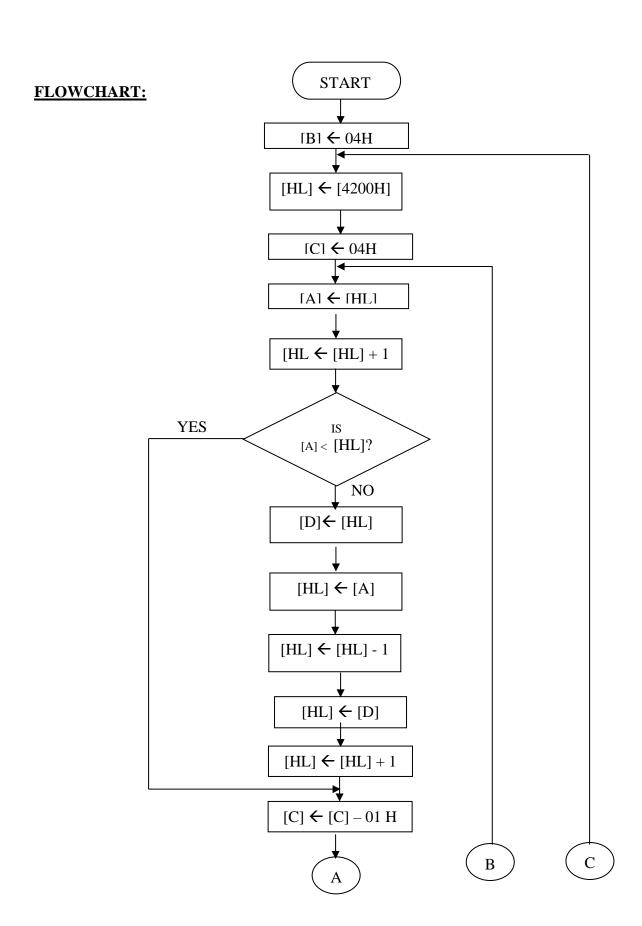

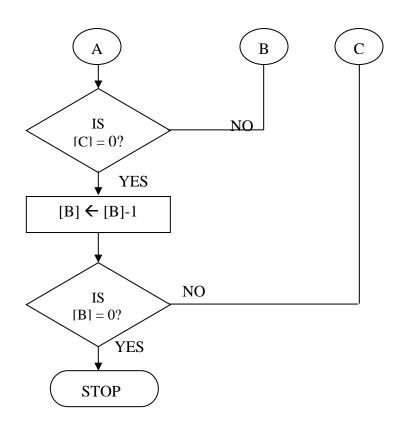

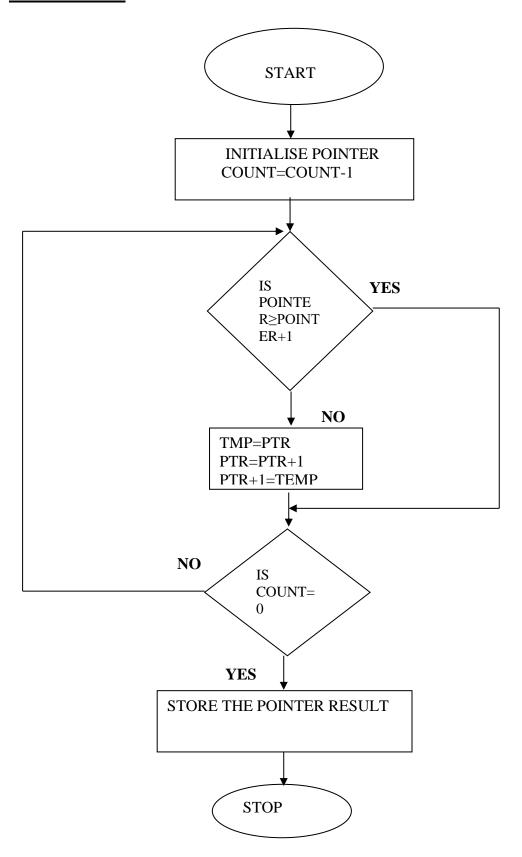

#### **2(C)** ASCENDING ORDER

#### AIM:

To sort the given numbers in the ascending order using 8085 microprocessor.

#### **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board

- 1. Get the numbers to be sorted from the memory locations.

- 2. Compare the first two numbers and if the first number is larger than second then interchange the number.

- 3. If the first number is smaller, go to step 4

- 4. Repeat steps 2 and 3 until the numbers are in required order

| ADDRES<br>S | OPCODE | LABEL  | MNEMONICS | OPERAND | COMMENTS                                        |

|-------------|--------|--------|-----------|---------|-------------------------------------------------|

| 4100        |        |        | MVI       | B,04    | Initialize B reg with                           |

| 4101        |        |        |           |         | number of comparisons (n-1)                     |

| 4102        |        | LOOP 3 | LXI       | H,4200  | Initialize HL reg. to                           |

| 4103        |        |        |           |         | 8100H                                           |

| 4104        |        |        |           |         |                                                 |

| 4105        |        |        | MVI       | C,04    | Initialize C reg with no.                       |

| 4106        |        |        |           |         | of comparisons(n-1)                             |

| 4107        |        | LOOP2  | MOV       | A,M     | Transfer first data to acc.                     |

| 4108        |        |        | INX       | Н       | Increment HL reg. to point next memory location |

| 4109        |        |        | CMP       | M       | Compare M & A                                   |

| 410A        |        |        | JC        | LOOP1   | If A is less than M then                        |

| 410B        |        |        |           |         | go to loop1                                     |

| 410C        |        |        |           |         |                                                 |

| 410D        |        |        | MOV       | D,M     | Transfer data from M to D reg                   |

| 410E        |        |        | MOV       | M,A     | Transfer data from acc to M                     |

| 410F        |        |        | DCX       | Н       | Decrement HL pair                               |

| 4110        |        |        | MOV       | M,D     | Transfer data from D to M                       |

| 4111        |        |        | INX       | Н       | Increment HL pair                               |

| 4112        |        | LOOP1  | DCR       | С       | Decrement C reg                                 |

| 4113        |        |        | JNZ       | LOOP2   | If C is not zero go to                          |

| 4114        |        |        |           |         | loop2                                           |

| 4115        |        |        |           |         |                                                 |

| 4116        |        |        | DCR       | В       | Decrement B reg                                 |

| 4117        |        |        | JNZ       | LOOP3   | If B is not Zero go to                          |

| 4118        |        |        |           |         | loop3                                           |

| 4119        |        |        |           |         |                                                 |

| 411A        |        |        | HLT       |         | Stop the program                                |

| IN       | PUT  | OUTPUT   |      |  |

|----------|------|----------|------|--|

| MEMORY   | DATA | MEMORY   | DATA |  |

| LOCATION |      | LOCATION |      |  |

| 4200     | 01   | 4200     | 01   |  |

| 4201     | 06   | 4201     | 02   |  |

| 4202     | 03   | 4202     | 03   |  |

| 4203     | 07   | 4203     | 06   |  |

| 4204     | 02   | 4204     | 07   |  |

#### **RESULT:**

Thus the ascending order program is executed and the numbers are arranged in ascending order.

#### **VIVA QUESTION:**

- 1. Explain INX operation

- 2. State the logic behind the Sorting an array of data in Descending order

- 3. What are the advantages of using memory segmentation 8085?

- 4. What is the macro & when it is used?

- 5. What is the function of direction flag?

- 6. What is DMA?

- 7. Define machine cycle and instruction cycle?

#### **FLOWCHART:**

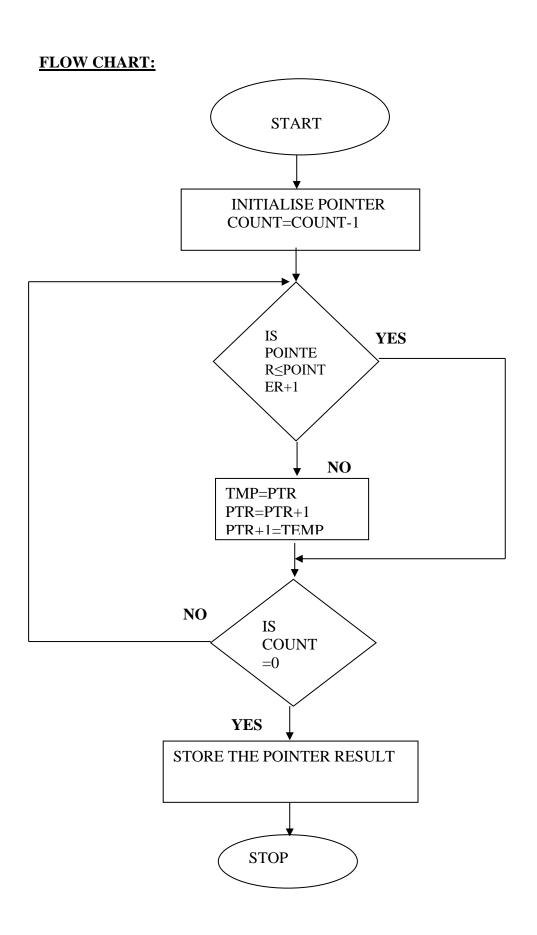

#### **2(D) DESCENDING ORDER**

#### AIM:

To sort the given numbers in the descending order using 8085 microprocessor.

#### **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board

- 1. Get the numbers to be sorted from the memory locations.

- 2. Compare the first two numbers and if the first number is smaller than second then interchange the number.

- 3. If the first number is larger, go to step 4

- 4. Repeat steps 2 and 3 until the numbers are in required order

| ADDRESS | OPCODE | LABEL | MNEMONICS | OPERAND | COMMENTS             |

|---------|--------|-------|-----------|---------|----------------------|

| 4100    |        |       | MVI       | B,04    | Initialize B reg     |

| 4101    |        |       |           |         | with number of       |

|         |        |       |           |         | comparisons (n-1)    |

| 4102    |        | LOOP  | LXI       | H,4200  | Initialize HL reg.   |

|         |        | 3     |           |         | to                   |

| 4103    |        |       |           |         | 8100H                |

| 4104    |        |       |           |         |                      |

| 4105    |        |       | MVI       | C,04    | Initialize C reg     |

| 4106    |        |       |           |         | with no. of          |

|         |        |       |           |         | comparisons(n-1)     |

| 4107    |        | LOOP2 | MOV       | A,M     | Transfer first data  |

|         |        |       |           |         | to acc.              |

| 4108    |        |       | INX       | Н       | Increment HL reg.    |

|         |        |       |           |         | to point next        |

|         |        |       |           |         | memory location      |

| 4109    |        |       | CMP       | M       | Compare M & A        |

| 410A    |        |       | JNC       | LOOP1   | If A is greater than |

| 410B    |        |       |           |         | M then go to loop1   |

| 410C    |        |       |           |         |                      |

| 410D    |        |       | MOV       | D,M     | Transfer data from   |

|         |        |       |           |         | M to D reg           |

| 410E    |        |       | MOV       | M,A     | Transfer data from   |

|         |        |       |           |         | acc to M             |

| 410F    |        |       | DCX       | Н       | Decrement HL         |

|         |        |       |           |         | pair                 |

| 4110    |        |       | MOV       | M,D     | Transfer data from   |

|         |        |       |           |         | D to M               |

| 4111    |        |       | INX       | Н       | Increment HL pair    |

| 4112    |        | LOOP1 | DCR       | C       | Decrement C reg      |

| 4113    |        |       | JNZ       | LOOP2   | If C is not zero go  |

| 4114    |        |       |           |         | to loop2             |

| 4115    |        |       |           |         |                      |

| 4116    |        |       | DCR       | В       | Decrement B reg      |

| 4117    |        |       | JNZ       | LOOP3   | If B is not Zero go  |

| 4118    |        |       |           |         | to loop3             |

| 4119    |        |       |           |         |                      |

| 411A    |        |       | HLT       |         | Stop the program     |

#### **OBSERVATION:**

| INPUT    |      | OUT      | PUT  |

|----------|------|----------|------|

| MEMORY   | DATA | MEMORY   | DATA |

| LOCATION |      | LOCATION |      |

| 4200     | 01   | 4200     | 07   |

| 4201     | 06   | 4201     | 06   |

| 4202     | 03   | 4202     | 03   |

| 4203     | 07   | 4203     | 02   |

| 4204     | 02   | 4204     | 01   |

#### **RESULT:**

Thus the descending order program is executed and the numbers are arranged in descending order.

## **VIVA QUESTION:**

- 1. Give out the purpose of the instruction DCX

- 2. What is meant by CALL instruction?

- 3. Briefly give out the LHLD instruction

- 4. State the logic behind the Sorting an array of data in Descending order

- 5. Name the various flag bits available in 8085 microprocessor?

- 6. Give the significance of SIM and RIM instructions available in 8085?

- 7. How do the address and data lines are demultiplexed in 8085?

## **FLOWCHART:**

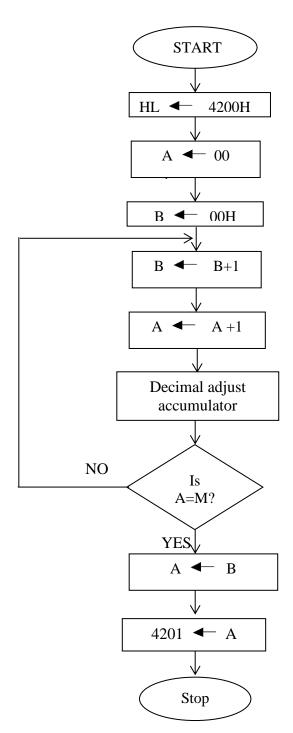

## 2(E) CODE CONVERSION - DECIMAL TO HEXADECIMAL

## AIM:

To convert a given decimal number to hexadecimal number.

#### **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board

#### **ALGORITHM:**

- 1. Initialize the memory location to the data pointer.

- 2. Increment B register.

- 3. Increment accumulator by 1 and adjust it to decimal every time.

- 4. Compare the given decimal number with accumulator value.

- 5. When both matches, the equivalent hexadecimal value is in B register.

- 6. Store the resultant in memory location.

| ADDRESS | OPCODE | LABEL | MNEMONICS | OPERAND | COMMENTS              |

|---------|--------|-------|-----------|---------|-----------------------|

| 4100    |        |       | LXI       | H,4200  | Initialize HL reg.    |

| 4101    |        |       |           |         | to 4200H              |

| 4102    |        |       |           |         |                       |

| 4103    |        |       | MVI       | A,00    | Initialize A          |

| 4104    |        |       |           |         | register.             |

| 4105    |        |       | MVI       | B,00    | Initialize B          |

| 4106    |        |       |           |         | register              |

| 4107    |        | LOOP  | INR       | В       | Increment B reg.      |

| 4108    |        |       | ADI       | 01      | Increment A reg       |

| 4109    |        |       |           |         |                       |

| 410A    |        |       | DAA       |         | Decimal Adjust        |

|         |        |       |           |         | Accumulator           |

| 410B    |        |       | CMP       | M       | Compare M & A         |

| 410C    |        |       | JNZ       | LOOP    | If acc and given      |

| 410D    |        |       |           |         | number are not        |

| 410E    |        |       |           |         | equal, then go to     |

|         |        |       |           |         | LOOP                  |

| 410F    |        |       | MOV       | A,B     | Transfer B reg to     |

|         |        |       |           |         | acc.                  |

| 4110    |        |       | STA       | 4201    | Store the result in a |

| 4111    |        |       |           |         | memory location.      |

| 4112    |        |       |           |         |                       |

| 4113    |        |       | HLT       |         | Stop the program      |

#### **OBSERVATION:**

| INF     | PUT  | OUT     | PUT  |

|---------|------|---------|------|

| ADDRESS | DATA | ADDRESS | DATA |

| 4200    | 21   | 4201    | 15   |

## **RESULT:**

Thus an ALP program for conversion of decimal to hexadecimal was written and executed.

#### **VIVA QUESTION:**

- 1. What is meant by ADI instruction?

- 2. What is the function of DAA instruction?

- 3. What is the function of XCHG instruction?

- 4. How you can load 16-bit data in 8500H and 8501H memory locations?

- 5. What is the difference between LHLD and SHLD instructions?

- 6. What is physical address?

- 7. Define OFFSET address.

## **FLOWCHART:**

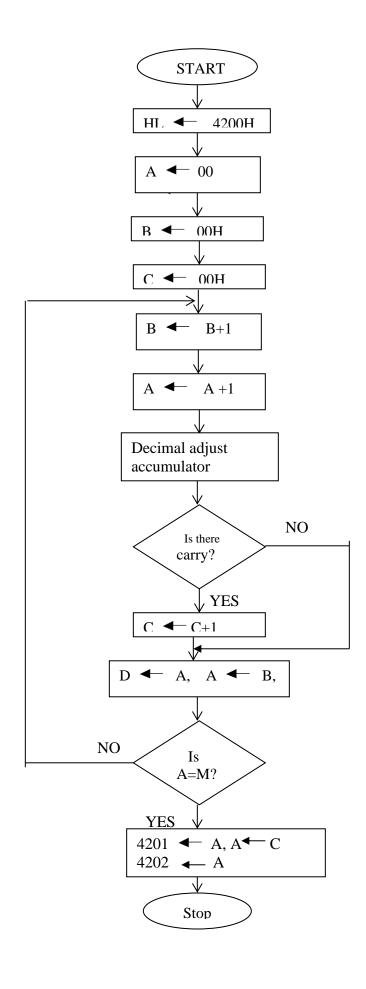

## 2(F) CODE CONVERSION - HEXADECIMAL TO DECIMAL

#### **AIM:**

To convert a given hexadecimal number to decimal number and also to verify the result.

#### **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board.

#### **ALGORITHM:**

- 1. Initialize the memory location to the data pointer.

- 2. Increment B register.

- 3. Increment accumulator by 1 and adjust it to decimal every time.

- 4. Compare the given hexadecimal number with B register value.

- 5. When both match, the equivalent decimal value is in A register.

- 6. Store the resultant in memory location.

| ADDRESS | OPCODE | LABEL | MNEMONICS | OPERAND | COMMENTS             |

|---------|--------|-------|-----------|---------|----------------------|

| 4100    |        |       | LXI       | H,4200  | Initialize HL reg.   |

|         |        |       |           |         | to                   |

|         |        |       |           |         | 8100H                |

| 4103    |        |       | MVI       | A,00    | Initialize A         |

|         |        |       |           |         | register.            |

| 4105    |        |       | MVI       | B,00    | Initialize B         |

| 4106    |        |       |           |         | register.            |

| 4107    |        |       | MVI       | C,00    | Initialize C         |

| 4108    |        |       |           |         | register for carry.  |

| 4109    |        | LOOP  | INR       | В       | Increment B reg.     |

| 410A    |        |       | ADI       | 01      | Increment A reg      |

| 410B    |        |       |           |         |                      |

| 410C    |        |       | DAA       |         | Decimal Adjust       |

|         |        |       |           |         | Accumulator          |

| 410D    |        |       | JNC       | NEXT    | If there is no carry |

|         |        |       |           |         | go to NEXT.          |

| 4110    |        |       | INR       | С       | Increment c          |

|         |        |       |           |         | register.            |

| 4111    |        | NEXT  | MOV       | D,A     | Transfer A to D      |

| 4112    |        |       | MOV       | A,B     | Transfer B to A      |

| 4113    |        |       | CMP       | M       | Compare M & A        |

| 4114    |        |       | MOV       | A,D     | Transfer D to A      |

| 4115    |        |       | JNZ       | LOOP    | If acc and given     |

|         |        |       |           |         | number are not       |

|         |        |       |           |         | equal, then go to    |

|         |        |       |           |         | LOOP                 |

| 4118    |        |       | STA       | 4201    | Store the result in  |

|         |        |       | ~ 111     | 01      | a memory             |

|         |        |       |           |         | location.            |

| 411B    |        |       | MOV       | A,C     | Transfer C to A      |

| 411C    |        |       | STA       | 4202    | Store the carry in   |

|         |        |       |           |         | another memory       |

|         |        |       |           |         | location.            |

| 411F    |        |       | HLT       |         | Stop the program     |

#### **OBSERVATION:**

| INPUT   |      | OUTPUT  |      |

|---------|------|---------|------|

| ADDRESS | DATA | ADDRESS | DATA |

| 4200    | D5   | 4201    | 13   |

|         |      | 4202    | 02   |

## **RESULT:**

Thus an ALP program for conversion of hexadecimal to decimal was executed and the result is verified.

## **VIVA QUESTIONS:**

- 1. What is meant by instruction DAA?

- 2. Why data bus is bi-directional?

- 3. Specifies the function of address bus and the direction of address bus?

- 4. How many memory location can be addressed by a microprocessor with the 14 address lines?

- 5. List various instructions that can be used to clear accumulator in 8085?

- 6. When the Ready signal of 8085 is sampled by the processor?

- 7. List out the similarities b/w the CALL\_RET and PUSH\_POP instructions?

## **FLOWCHART:**

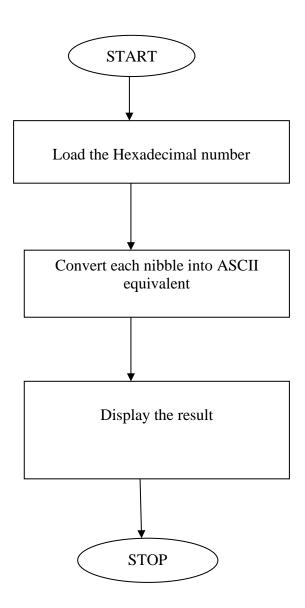

## 2(G). CODE CONVERSION –HEXADECIMAL TO ASCII

#### Aim

To write an assembly language program to covert the given Hexadecimal number into its ASCII equivalent and to verify the result.

## **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board.

## Algorithm:

- Step 1: Load the Hexadecimal number from the location

- Step 2: Separate the nibbles

- Step 3: Convert each nibble to its ASCII Equivalent.

- Step 4: Add the two converted values

- Step 5: Display the result

- Step 6: Stop

| ADDRESS | OPCODE | LABEL | MNEMONICS | OPERAND | COMMEN<br>TS                   |

|---------|--------|-------|-----------|---------|--------------------------------|

| 4100    |        |       | LDA       | 4200    | Get the data                   |

| 4101    |        |       |           |         |                                |

| 4102    |        |       |           |         |                                |

| 4103    |        |       | MOV       | B,A     |                                |

| 4104    |        |       | ANI       | OF      | Mask upper                     |

| 4105    |        |       | CATA      | GLID    | nibble                         |

| 4106    |        |       | CALL      | SUB     | Get ASCII                      |

| 4107    |        |       |           |         | code for                       |

| 4108    |        |       |           |         | upper nibble                   |

| 4109    |        |       | STA       | 4201    | Store the                      |

| 410A    |        |       |           |         | value of accumulator           |

| 410B    |        |       |           |         |                                |

| 410C    |        |       | MOV       | A,B     | Mov B reg<br>content to<br>Acc |

| 410D    |        |       | ANI       | F0      | Mask lower                     |

| 410E    |        |       |           |         | nibble                         |

| 410F    |        |       | RLC       |         | Rotate left                    |

| 4110    |        |       | RLC       |         | with out                       |

| 4111    |        |       | RLC       |         | carry 4                        |

| 4112    |        |       | RLC       |         | times                          |

| 4113    |        |       | CALL      | SUB     | Get the                        |

| 4114    |        |       |           |         | ASCII code                     |

| 4115    |        |       |           |         | -                              |

| 4116    |        |       | STA       | 4202    | Store the                      |

| 4117    |        |       |           |         | accumulator                    |

| 4118    |        |       |           |         |                                |

| 4119    |        |       | HLT       |         | Stop                           |

| 411A    |        | SUB   | CPI       | 0A      | Compare                        |

| 411B    |        |       |           |         | with OA                        |

| 411C    |        |       | JC        | SKP     | Skip if carry                  |

| 411D    |        |       |           |         | 1 ,                            |

| 411E    |        |       |           |         |                                |

| 411F    |        |       | ADI       | 07      | Add 07 to                      |

| 4120    |        |       |           |         | Acc                            |

| 4121    |        | SKP   | ADI       | 30      | Add 30 to                      |

| 4122    |        |       |           |         | Acc                            |

| 4123    |        |       | RET       |         | Return                         |

## **OBSERVATION:**

| INPUT   |      | OUTPUT  |      |

|---------|------|---------|------|

| ADDRESS | DATA | ADDRESS | DATA |

| 4200    | A5   | 4201    | 35   |

|         |      | 4202    | 41   |

#### **Result:**

Thus assembly language program to covert the given Hexadecimal number into its ASCII equivalent is completed and also the result is verified.

## **VIVA QUESTIONS:**

- 1. What is ASCII number for OAH?

- 2. What is difference between byte and word?

- 3. What is the immediate addressing mode?

- 4. What are data transfer instructions?

- 5. What is the use of immediate addressing mode?

- 6. What are branching instructions?

- 7. What is DMA?

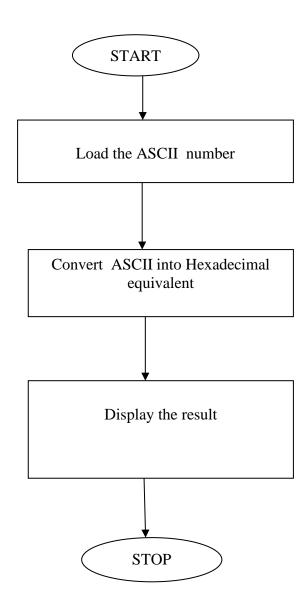

## **FLOW CHART:**

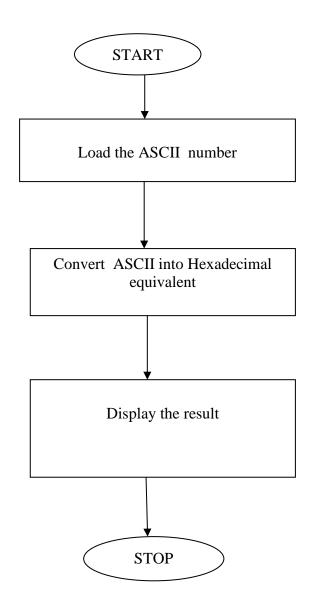

## 2(H). CODE CONVERSION – ASCII TO HEXADECIMAL

#### AIM:

To write an assembly language program to covert the given ASCII number into its Hexadecimal equivalent and to verify the result.

## **APPARATUS REQUIRED:**

8085 microprocessor kit ,key board.

#### **ALGORITHM:**

- Step 1: Load the ASCII number from the location

- Step 2: Check for the digit or alphabet

- Step 3: Using suitable logic and instructions convert the ASCIII number into Hexadecimal

- Step 4: Add the two converted values

- Step 5: Display the result

- Step 6: Stop

| ADDRESS | OPCODE | LABEL | MNEMONICS | OPERAND | COMMENTS            |

|---------|--------|-------|-----------|---------|---------------------|

| 4100    |        |       | LDA       | 4500    | Load the            |

| 4102    |        |       |           |         | memory content to   |

| 4102    |        |       |           |         | Accumulator         |

| 4103    |        |       | SUI       | 30      | Subtract with       |

| 4104    |        |       |           |         | 30                  |

| 4105    |        |       | CPI       | 0A      | Compare with        |

| 4106    |        |       |           |         | OA                  |

| 4107    |        |       | JC        | SKP     | If carry skip       |

| 4108    |        |       |           |         |                     |

| 4109    |        |       |           |         |                     |

| 410A    |        |       | SUI       | 07      | Subtract with 07    |

| 410B    |        |       |           |         |                     |

| 410C    |        | SKP   | STA       | 4201    | Store               |

| 410D    |        |       |           |         | Accumulator content |

| 410E    |        |       |           |         |                     |

| 410F    |        |       | HLT       |         | Stop                |

#### **OBSERVATION:**

| INPUT   |      | OUTPUT  |      |

|---------|------|---------|------|

| ADDRESS | DATA | ADDRESS | DATA |

| 4200    | 41   | 4201    | 0A   |

#### **Result:**

Thus assembly language program to covert the given ASCII number into its Hexadecimal equivalent is completed and also the result is verified.

## **VIVA QUESTIONS:**

- 1. What is the Hexadecimal for (35)<sub>ASCII</sub>?

- 2. What is the purpose of branch instructions in 8085 microprocessor?

- 3. Define one's complement of an 8-bit numbers

- 4. What is the function of CMA instruction?

- 5. What is the logic behind the conversion of ASCII number into Hexadecimal number.

- 6. Give example for Machine control instruction?

- 7. What is the need of code conversion?

#### **FLOW CHART:**

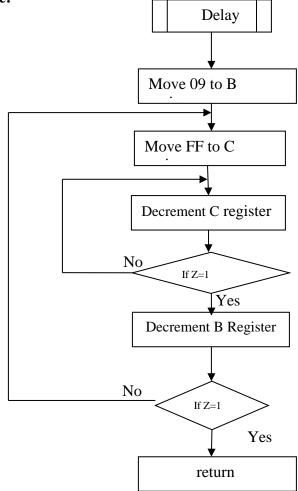

## **Delay Subroutine:**

#### 3A INTERFACING ANALOG TO DIGITAL CONVERTER

#### AIM:

To write an assembly language program to convert an analog signal into a digital signal using an ADC interfacing.

#### **APPARATUS REQUIRED:**

| SL.NO | ITEM                | SPECIFICATION    | QUANTITY |

|-------|---------------------|------------------|----------|

| 1.    | Microprocessor kit  | 8085             | 1        |

| 2.    | Power Supply        | +5 V dc,+12 V dc | 1        |

| 3.    | ADC Interface board | -                | 1        |

#### **PROBLEM STATEMENT:**

The program is executed for various values of analog voltage which are set with the help of a potentiometer. The LED display is verified with the digital value that is stored in a memory location.

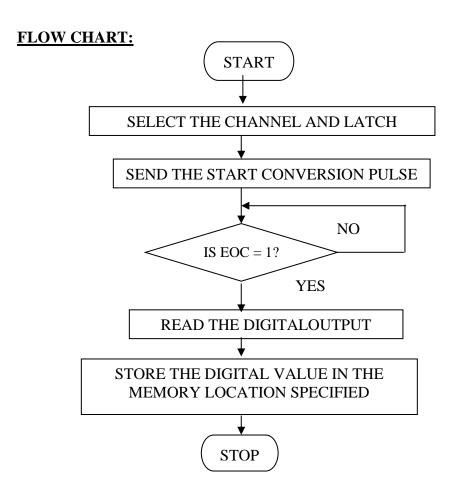

#### THEORY:

An ADC usually has two additional control lines: the SOC input to tell the ADC when to start the conversion and the EOC output to announce when the conversion is complete. The following program initiates the conversion process, checks the EOC pin of ADC 0809 as to whether the conversion is over and then inputs the data to the processor. It also instructs the processor to store the converted digital data at RAM location.

#### **ALGORITHM:**

- 1. Select the channel and latch the address.

- 2. Send the start conversion pulse.

- 3. Read EOC signal.

- 4. If EOC = 1 continue else go to step (3)

- 5. Read the digital output.

- 6. Store it in a memory location.

| ADDRESSS | LABEL | OPCODE | MNEMONICS | COMMENTS                                                                |

|----------|-------|--------|-----------|-------------------------------------------------------------------------|

| 4100     |       |        | MVI A,10H | Select channel                                                          |

| 4102     |       |        | OUT C8    | Send through output port                                                |

| 4103     |       |        | MVI A,18H | Load accumulator with value for ALE low                                 |

| 4105     |       |        | OUT C8    | Send through output port                                                |

| 4106     |       |        | MVI A,01H | Store the value to make SOC high in the accumulator                     |

| 4108     |       |        | OUT 00H   | Send through output port                                                |

| 4109     |       |        | XRA A     |                                                                         |

| 410A     |       |        | XRA A     | Introduce delay                                                         |

| 410B     |       |        | XRA A     |                                                                         |

| 410C     |       |        | MVI A,00  | Store the value to make SOC low the accumulator                         |

| 410E     |       |        | OUT D0H   | Send through output port                                                |

| 410F     | L1    |        | IN D8H    |                                                                         |

| 4110     |       |        | ANI 01    | Read the EOC signal                                                     |

| 4112     |       |        | CPI 01    | from port & check for end of conversion                                 |

| 4114     |       |        | JNZ L1    | If the conversion is not yet completed, read EOC signal from port again |

| 4117     |       |        | IN C0H    | Read data from port                                                     |

| 4118     |       |        | STA 4150H | Store the data                                                          |

| 411B     |       |        | HLT       | Stop                                                                    |

## **OBSERVATION:**

| ANALOG      | DIGITAL DATA ON LED | HEX CODE IN MEMORY |

|-------------|---------------------|--------------------|

| VOLTAGE (V) | DISPLAY             | LOCATION           |

| 5           | 1111 1111           | FF                 |

| 0           | 0000 0000           | 00                 |

| 2.5         | 1000 0000           | 80                 |

## **RESULT:**

Thus the ADC was interfaced with 8085and the given analog inputs were converted into its digital equivalent.

| <u>VI</u> | VA QUESTIONS:                                                                                        |  |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1.        | What is the name given to time taken by the ADC from the active edge of SOC(start of                 |  |  |  |  |  |  |

|           | conversion) pulse till the active edge of EOC(end of conversion) signal?                             |  |  |  |  |  |  |

| 2.        | What are the popular technique that is used in the integration of ADC chips?                         |  |  |  |  |  |  |

| 3.        | The procedure of algorithm for interfacing ADC contain                                               |  |  |  |  |  |  |

| 4.        | Which is the ADC among the following?                                                                |  |  |  |  |  |  |

|           | a) AD 7523 b) 74373 c) 74245 d) ICL7109                                                              |  |  |  |  |  |  |

| 5.        | The conversion delay in successive approximation of an ADC 0808/0809 is                              |  |  |  |  |  |  |

| 6.        | The number of inputs that can be connected at a time to an ADC that is integrated with               |  |  |  |  |  |  |

|           | successive approximation is                                                                          |  |  |  |  |  |  |

| 7.        | ADC 7109 integrated by Dual slope integration technique is used for                                  |  |  |  |  |  |  |

|           |                                                                                                      |  |  |  |  |  |  |

| 8.        | Which of the following is not one of the phase of total conversion cycle?                            |  |  |  |  |  |  |

| 9.        | Which of the following phase contain feedback loop in it?                                            |  |  |  |  |  |  |

|           | a) auto zero phase b) signal integrate phase                                                         |  |  |  |  |  |  |

|           | c) deintegrate phase d) none                                                                         |  |  |  |  |  |  |

| 10.       | <b>0.</b> In the signal integrate phase, the differential input voltage between IN LO(input low) and |  |  |  |  |  |  |

| IN        |                                                                                                      |  |  |  |  |  |  |

|           | HI(input high) pins is integrated by the internal integrator for a fixed period of                   |  |  |  |  |  |  |

|           |                                                                                                      |  |  |  |  |  |  |

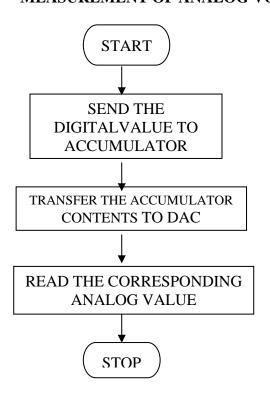

## **FLOWCHART: MEASUREMENT OF ANALOG VOLTAGE**

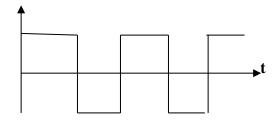

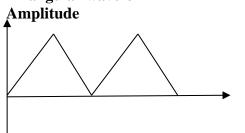

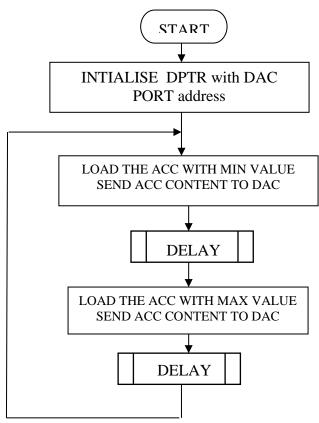

#### TRIANGULAR WAVE FORM

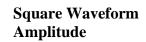

## **SQUARE WAVE FORM**

#### 3B INTERFACING DIGITAL TO ANALOG CONVERTER

#### AIM:

- 1. To write an assembly language program for digital to analog conversion

- 2. To convert digital inputs into analog outputs & to generate different waveforms

#### **APPARATUS REQUIRED:**

| SL.NO | ITEM                | SPECIFICATION        | QUANTITY |

|-------|---------------------|----------------------|----------|

| 1.    | Microprocessor kit  | 8086 Vi Microsystems | 1        |

| 2.    | Power Supply        | +5 V, dc,+12 V dc    | 1        |

| 3.    | DAC Interface board | -                    | 1        |

#### **PROBLEM STATEMENT:**

The program is executed for various digital values and equivalent analog voltages are measured and also the waveforms are measured at the output ports using CRO.

#### THEORY:

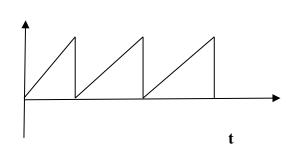

Since DAC 0800 is an 8 bit DAC and the output voltage variation is between –5v and +5v. The output voltage varies in steps of 10/256 = 0.04 (approximately). The digital data input and the corresponding output voltages are presented in the table. The basic idea behind the generation of waveforms is the continuous generation of analog output of DAC. With 00 (Hex) as input to DAC2 the analog output is –5v. Similarly with FF H as input, the output is +5v. Outputting digital data 00 and FF at regular intervals, to DAC2, results in a square wave of amplitude 5v.Output digital data from 00 to FF in constant steps of 01 to DAC2. Repeat this sequence again and again. As a result a saw-tooth wave will be generated at DAC2 output. Output digital data from 00 to FF in constant steps of 01 to DAC2. Repeat this sequence again and again. As a result a triangular wave will be generated at DAC2 output.

#### **ALGORITHM:**

#### Measurement of analog voltage:

- 1. Send the digital value of DAC.

- 2. Read the corresponding analog value of its output.

#### **Waveform generation:**

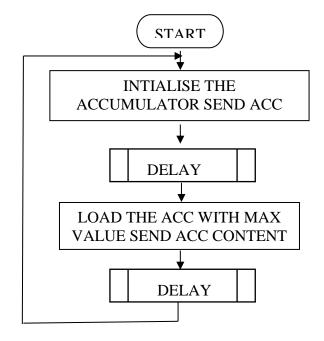

#### **Square Waveform:**

- 1. Send low value (00) to the DAC.

- 2. Introduce suitable delay.

- 3. Send high value to DAC.

- 4. Introduce delay.

- 5. Repeat the above procedure.

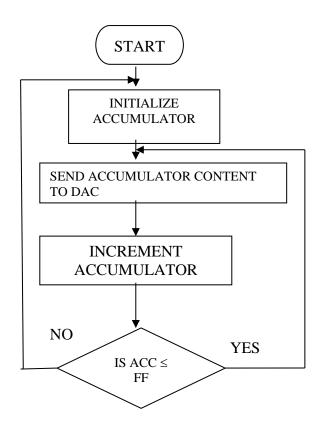

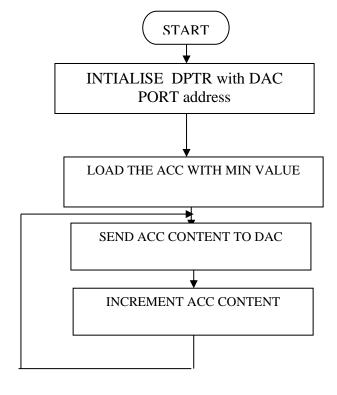

#### Saw-tooth waveform:

- 1. Load low value (00) to accumulator.

- 2. Send this value to DAC.

- 3. Increment the accumulator.

- 4. Repeat step (2) and (3) until accumulator value reaches FF.

- 5. Repeat the above procedure from step 1.

#### **SAWTOOTH WAVEFORM**

## **PROGRAM:** Measurement of Analog Voltage

| PROGRAM   | COMMENTS                             |

|-----------|--------------------------------------|

| MOV A,7FH | Load digital value 00 in accumulator |

| OUT C0    | Send through output port             |

| HLT       | Stop                                 |

## **OBSERVATION: Measurement of Analog Voltage**

| DIGITAL DATA | ANALOG VOLTAGE |

|--------------|----------------|

| FF           | 5 <b>V</b>     |

| 00           | $\mathbf{0V}$  |

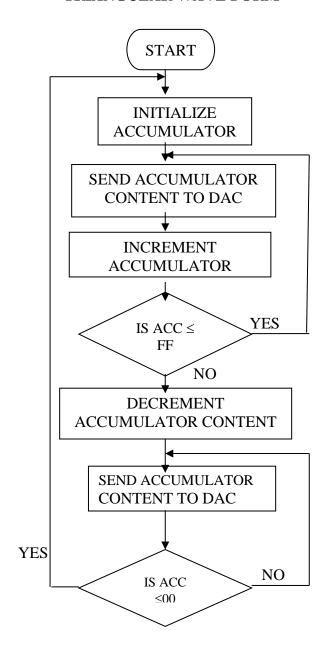

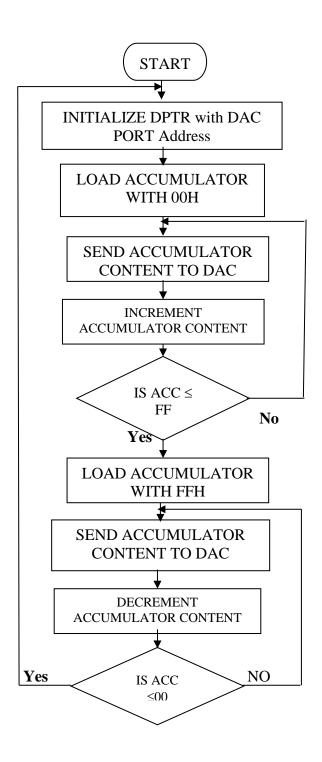

## **Triangular waveform:**

- 1. Load the low value (00) in accumulator.

- 2. Send this accumulator content to DAC.

- 3. Increment the accumulator.

- 4. Repeat step 2 and 3 until the accumulator reaches FF, decrement the accumulator and

- send the accumulator contents to DAC.

- 5. Decrementing and sending the accumulator contents to DAC.

- 6. The above procedure is repeated from step (1)

## **PROGRAM:** Square Wave

| ADDRESSS | LABEL | PROGRAM    | COMMENTS                          |

|----------|-------|------------|-----------------------------------|

| 4100     | START | MVI A,00H  | Load 00 in accumulator            |

| 4102     |       | OUT C8     | Send through output port          |

| 4103     |       | CALL DELAY | Give a delay                      |

| 4105     |       | MVI A,0FH  | Load 0F in accumulator            |

| 4107     |       | OUT C8     | Send through output port          |

| 4108     |       | CALL DELAY | Give a delay                      |

| 4109     |       | JMP START  | Go to starting location           |

| 410A     | DELAY | MVI B,05   | Load count value 05 in B register |

| 410B     | L1    | MVI C,0F   | Load count value 0F in B register |

| 410C     | L2    | DCR C      | Decrement C register              |

| 410E     |       | JNZ L2     | Return to loop2                   |

| 410F     |       | DCR B      | Decrement B register              |

| 4110     |       | JNZ L1     | Return to loop1                   |

| 4112     |       | RET        | Return to main program            |

## **PROGRAM:** Saw tooth Wave

| ADDRESSS | LABEL | PROGRAM   | COMMENTS                                     |

|----------|-------|-----------|----------------------------------------------|

| 4100     | START | MVI A,00H | Load 00 in accumulator                       |

| 4102     | L1    | OUT C0    | Send through output port                     |

| 4103     |       | INR A     | Increment contents of accumulator            |

| 4104     |       | JNZ L1    | Send through output port until it reaches FF |

| 4107     |       | JMP START | Go to starting location                      |

## **PROGRAM:** Triangular Wave

| ADDRESSS | LABEL | PROGRAM   | COMMENTS                                     |

|----------|-------|-----------|----------------------------------------------|

| 4100     | START | MVI L,00H | Load 00 in accumulator                       |

| 4102     | L1    | MOV A ,L  | Move contents of L to A                      |

| 4103     |       | OUT C8    | Send through output port                     |

| 4104     |       | INR C     | Increment contents of accumulator            |

| 4105     |       | JNZ L1    | Send through output port until it reaches FF |

| 4108     |       | MVI C,FFH | Load FF in accumulator                       |

| 4109 | L2 | MOV A,L   | Move contents of L to A                      |

|------|----|-----------|----------------------------------------------|

| 410A |    | OUT C8    | Send through output port                     |

| 410B |    | DCR C     | Decrement contents of accumulator            |

| 410C |    | JNZ L2    | Send through output port until it reaches 00 |

| 410F |    | JMP START | Go to starting location                      |

## **MODEL GRAPH:**

## Saw-tooth waveform Amplitude

## **RESULT OF WAVEFORM GENERATION:**

| WAVEFORMS              | AMPLITUDE | TIMEPERIOD |

|------------------------|-----------|------------|

| Square<br>Waveform     |           |            |

| Saw-tooth<br>waveform  |           |            |

| Triangular<br>waveform |           |            |

#### **RESULT:**

Thus digital to analog conversion is done and different waveforms such as square wave, sawtooth wave and triangular wave are generated by interfacing DAC with 8085

#### **VIVA QUESTIONS:**

- 1. DAC (Digital to Analog Converter) finds application in (digitally controlled gains,motor—speed controls, programmable gain amplifiers)

- 2. To save the DAC from negative transients the device connected between OUT1 and OUT2 of AD 7523 is \_\_\_\_\_\_

- 3. An operational amplifier connected to the output of AD 7523 is used (to convert current

- output to output voltage , to provide additional driving capability, as current-to-voltage converter)

- 4. The DAC 0800 has a settling time of (100 milliseconds).

- 5. What is meant by the instruction OUT C8

- 6. Give examples for various DAC ICs?

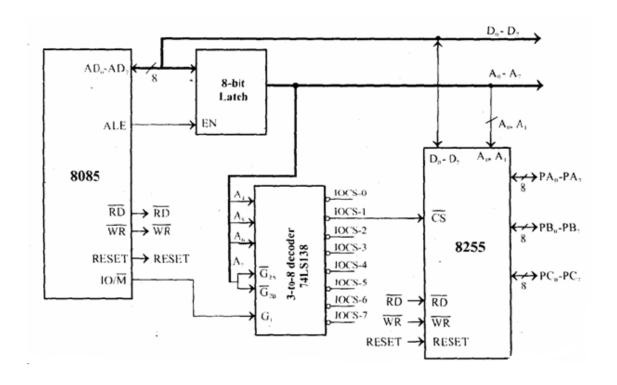

# 3C . TRAFFIC LIGHT CONTROLLER - INTERFACING PPI 8255 WITH 8085

## AIM:

To design traffic light controller using 8085 microprocessor through programmable peripheral interface 8255.

#### **APPARATUS REQUIRED:**

$8085~\mu p$  kit, 8255 Interface board, DC regulated power supply, VXT parallel bus, Traffic light controller interface board.

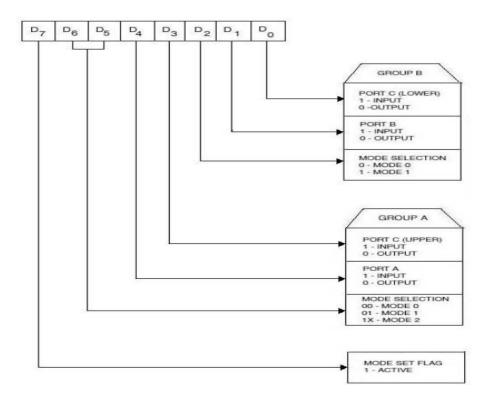

#### **I/O MODES:**

#### **MODE 0 – SIMPLE I/O MODE:**

This mode provides simple I/O operations for each of the three ports and is suitable for synchronous data transfer. In this mode all the ports can be configured either as input or output port.

Let us initialize port A as input port and port B as output port

#### **Control Word:**

| ADDRESS | OPCODES | LABEL | MNEMONICS | OPERAND | COMMENTS                      |

|---------|---------|-------|-----------|---------|-------------------------------|

| 4100    |         |       | LXI       | H,      | Load the data in HL           |

|         |         |       |           | Data    | register pair                 |

| 4103    |         |       | MVI       | C,04    | Move 04 to c register         |

| 4105    |         |       | MOV       | A,M     | Move M to A                   |

| 4106    |         |       | OUT       | CNT     | Out tocontrol register        |

| 4108    |         |       | INX       | Н       | Increment HL register pair    |

| 4109    |         | LOOP1 | MOV       | A,M     | Move M to A                   |

| 410A    |         |       | OUT       | CPRT    | Send control status<br>word   |

| 410C    |         |       | INX       | Н       | Increment h register          |

| 410D    |         |       | MOV       | A,M     | Move M to A                   |

| 410E    |         |       | OUT       | BPRT    | Send control status<br>word   |

| 4110    |         |       | INX       | Н       | Increment h register          |

| 4111    |         |       | MOV       | A,M     | Move M to A                   |

| 4112    |         |       | OUT       | APRT    | Send control status<br>word   |

| 4114    |         |       | CALL      | DELAY   | Call subroutine               |

| 4117    |         |       | INX       | Н       | Increment h register          |

| 4118    |         |       | DCR       | С       | Decrement C register          |

| 4119    |         |       | JNZ       | LOOP1   | Jump on nozero to loop1       |

| 411C    |         |       | JMP       | START   | Jump to start                 |

| 411F    |         | DELAY | PUSH      | В       | •                             |

| 4120    |         |       | MVI       | C.0D    | Move OD to C register         |

| 4122    |         | LOOP3 | LXI       | D,FF,FF | Load Dregister with FF        |

| 4125    |         | LOOP2 | DCX       | D       | Decrement Dregister           |

| 4126    |         |       | MOV       | A,D     | Move D contents to A register |

| 4127    |         |       | ORA       | Е       | OR the content of A with E    |

| 4128    |         |       | JNZ       | LOOP2   | Jump on nozero to loop2       |

| 412C    |         |       | JNZ       | LOOP3   | Jump on nozero to loop3       |

| 412F    |         |       | POP       | В       | Do pop operation              |

| 4130    |         |       | RET       |         | Return to main program        |

#### **MODE 1 STROBED I/O MODE:**

In this mode, port A and port B are used as data ports and port C is used as control signals for strobed I/O data transfer.

Let us initialize port A as input port in mode1

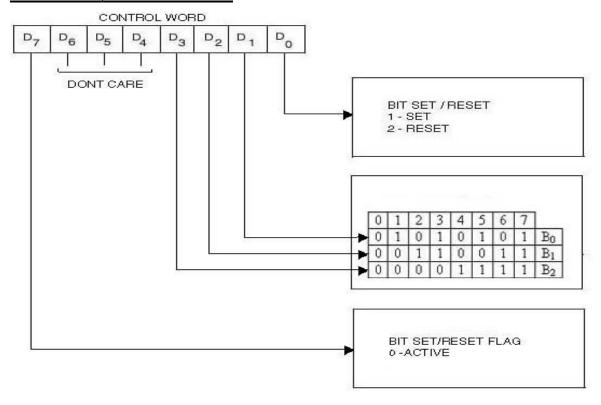

#### **BSR MODE** (Bit Set Reset mode

Any lines of port c can be set or reset individually without affecting other lines using this mode. Let us set PC0 and PC3 bits using this mode.

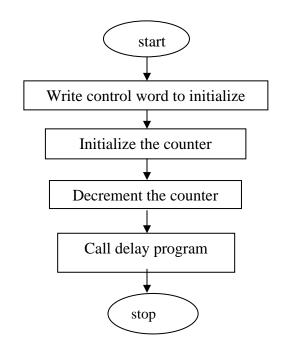

#### **ALGORITHM:-**

- 1. Start.

- 2. Write the control word to initialize 8255. Obtain the data for each direction and store in the memory.

- 3. Initialize a counter to indicate the number of directions.

- 4. Initialize HL Pair to the starting address of the data..

- 5. Check the result.